## **DUEPROLOGIC**

# FPGA DEVELOPMENT SYSTEM User Manual

The DueProLogic (DPL) and its integrated development and distinctive runtime environment has been specifically designed for Electrical Engineering students, hobbyists, and entrepreneurs prototyping/developing/running projects involving logic, with the added opportunity, of readily mating with a widely used microprocessor board, the Arduino Due, and other ARM Cortex compatibles. The combination of FPGA programmable logic and a microcontroller is unbeatable in an educational student learning setting and in many other projects where each can bring its strength.

The DPL FPGA development system provides a convenient, user-friendly work flow by connecting seamlessly with Altera's Quartus Prime software. The user will develop the code in the Quartus environment on a Windows Personal Computer. The programmable logic code is loaded into the FPGA using only the Quartus Programmer tool and a standard USB cable. The Active Host SDK provides a highly configurable bi-directional communications interface between Arduino and host. It connects transparently with the Active Transfer Library in the FPGA code. This Active Host/Active Transfer combination eliminates the complexity of designing a USB communication system. No scheduling USB transfers, USB driver interface or inf file changes are needed. The EPT FPGA development system is a unique combination of hardware and software.

Circuit designs, software and documentation are copyright © 2024, Earth People Technology, Inc

http://www.earthpeopletechnology.com/

# **Table of Contents**

| _ |         |                                              |     |

|---|---------|----------------------------------------------|-----|

| 1 | Introdu | ction and General Description                | 4   |

|   |         | est Driving the Active Host Test Application |     |

|   | 1.2 Ha  | ardware Description                          | 25  |

|   | 1.2.1   | Host PC Connection                           |     |

|   | 1.2.2   | CONF DONE LED                                | 29  |

|   | 1.2.3   | Jumper Settings                              | 31  |

|   | 1.2.4   | Inputs and Outputs                           |     |

|   | 1.2.5   | FPGA Configuration                           |     |

|   | 1.2.6   | FT2232H Dual Channel USB to Serial Chip      | 38  |

|   | 1.2.7   | SD Card Interface                            | 39  |

|   | 1.2.8   | SD Card Protocol                             | 41  |

|   | 1.2.9   | LEDs                                         | 48  |

|   | 1.2.10  | Pushbuttons                                  | 50  |

|   | 1.2.11  | Power Options                                | 53  |

|   | 1.2.12  | Clock Domains                                | 53  |

|   | 1.2.13  | JTAG Header                                  | 55  |

|   | 1.2.14  | PMOD Connectors                              | 56  |

|   | 1.2.15  | Slide Switches                               | 59  |

|   | 1.3 FP  | PGA Active Host Development                  | 61  |

|   | 1.4 Ac  | ctive Host EndTerms                          | 62  |

|   | 1.5 Ac  | ctive Transfer EndTerms                      | 66  |

| 2 | EPT Dr  | rivers                                       | 66  |

|   | 2.1 US  | SB Driver                                    | 67  |

|   | 2.2 JT  | AG DLL Insert to Quartus Prime Lite          | 70  |

|   | 2.2.1   | Installing Quartus                           | 70  |

|   | 2.2.2   | Downloading Quartus                          | 70  |

|   | 2.2.3   | Quartus Installer                            |     |

|   | 2.2.4   | Adding the EPT_Blaster to Quartus Prime      | 84  |

|   | 2.3 Ac  | ctive Host Application SDK                   | 85  |

| 3 | FPGA A  | Active Transfer Library                      | 90  |

|   |         | PT Active Transfer System Overview           |     |

|   |         | ctive Transfer Library                       |     |

|   | 3.2.1   | Active Trigger EndTerm                       |     |

|   | 3.2.2   | Active Transfer EndTerm                      |     |

|   | 3.2.3   | Active Block EndTerm                         |     |

|   |         | ming Diagram for Active Transfer EndTerms    |     |

|   | 3.3.1   | Active Trigger EndTerm Timing                |     |

|   | 3.3.2   | Active Transfer EndTerm Timing               | 104 |

|   | 3.3.3    | Active Block EndTerm Timing                            |     |

|---|----------|--------------------------------------------------------|-----|

| 4 | Compili  | ng, Synthesizing, and Programming FPGA                 | 106 |

|   |          | ting up the Project and Compiling                      |     |

|   | 4.1.1    | Selecting Pins and Synthesizing                        | 115 |

|   | 4.1.2    | Configuring the FPGA                                   | 124 |

| 5 | Active F | Host Application                                       | 136 |

|   | 5.1 Tri  | gger EndTerm                                           | 138 |

|   | 5.2 Tra  | nsfer(Byte) EndTerm                                    | 138 |

|   | 5.3 Blo  | ock EndTerm                                            | 138 |

|   | 5.4 Act  | rive Host SDK                                          | 139 |

|   | 5.4.1    | Active Host Open Device                                | 139 |

|   | 5.4.2    | Active Host Data Received Function                     | 142 |

|   | 5.4.3    | Active Host Triggers                                   |     |

|   | 5.4.4    | Active Host Byte Transfers                             |     |

|   | 5.4.5    | Active Host Block Transfers                            |     |

| 6 | Assemb   | ling, Building, and Executing a .NET Project on the PC | 152 |

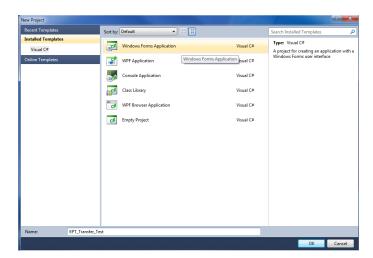

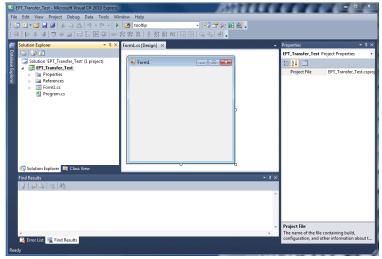

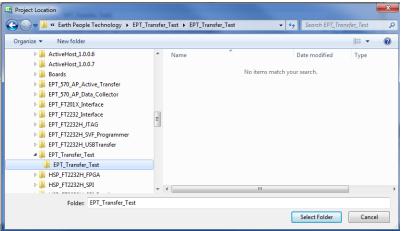

|   | 6.1 Cre  | eating a Project                                       |     |

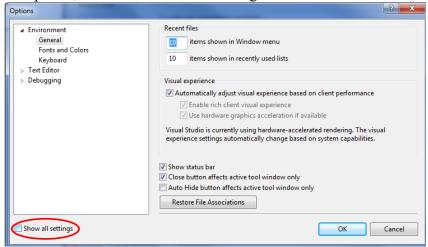

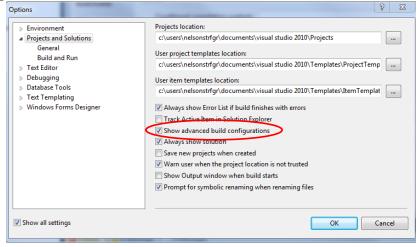

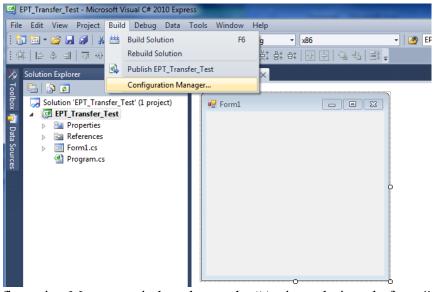

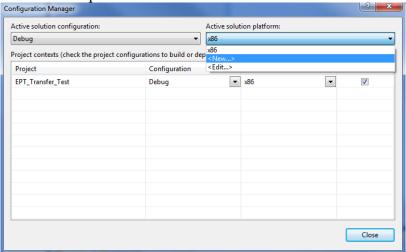

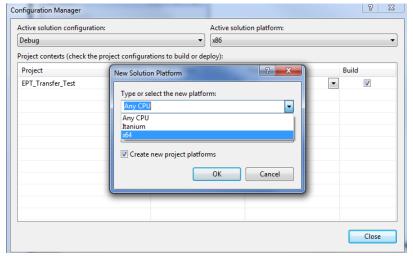

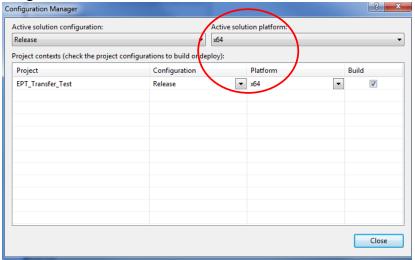

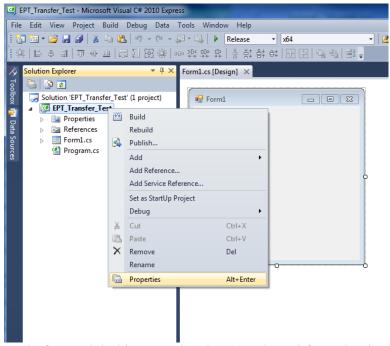

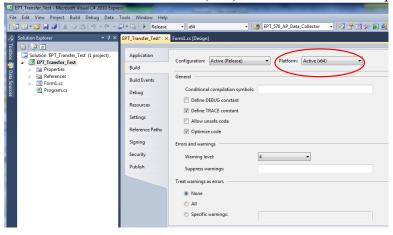

|   | 6.1.1    | Setting up the C# Express Environment x64 bit          | 154 |

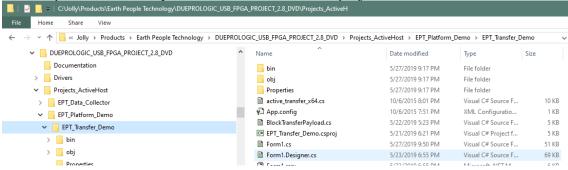

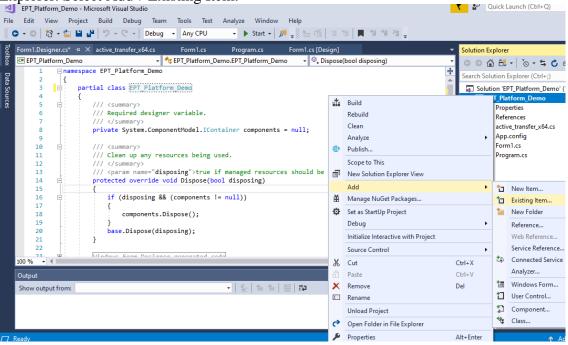

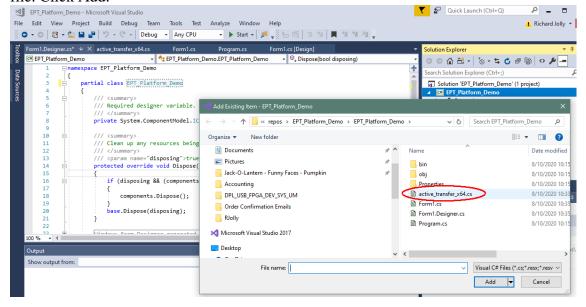

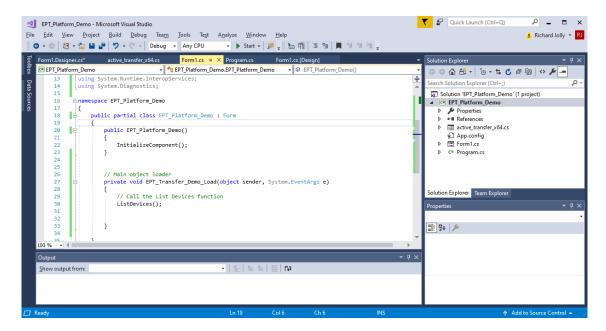

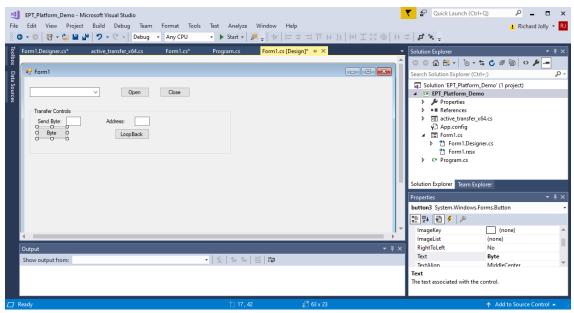

|   | 6.2 Ass  | sembling Files into the Project                        | 161 |

|   | 6.2.1    | Changing Project Name                                  |     |

|   | 6.2.2    | Add Files to Project                                   |     |

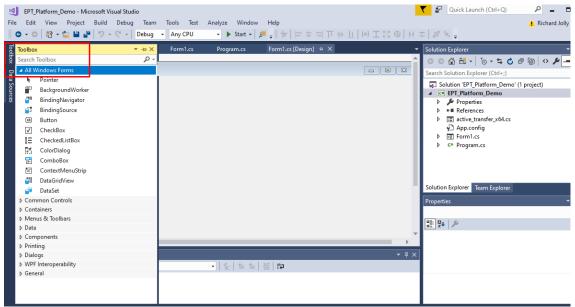

|   | 6.2.3    | Adding Controls to the Project                         |     |

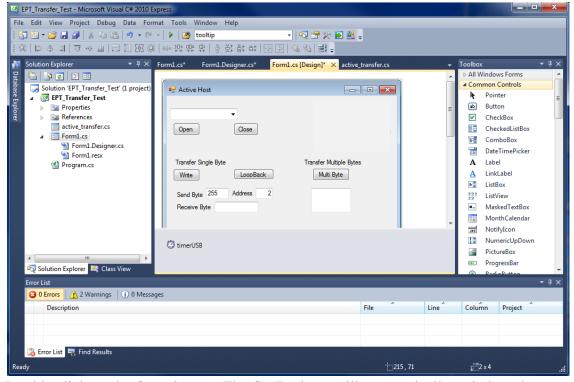

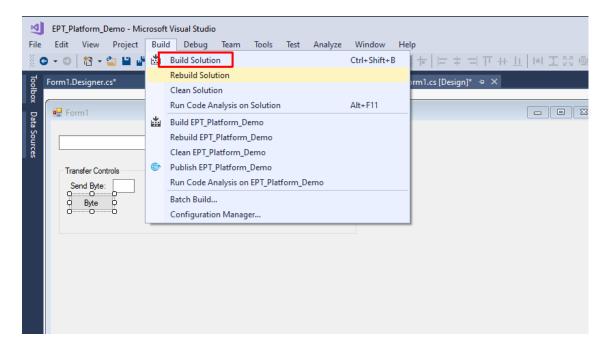

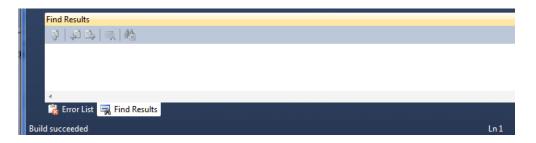

|   | 6.2.4    | Building the Project                                   | 170 |

|   | 6.2.5    | Testing the Project                                    | 171 |

# 1 Introduction and General Description

The DueProLogic gives learners the opportunity to have a hands-on approach when learning logic, exploring different iterations of schematic/code designs and the operation of those circuits.

With the DPL's FPGA, projects can be easily be attempted which rely on asynchronous, exceedingly fast, and even multiple separate concurrent logic structures operating in parallel. Logic circuits are implemented within the FPGA at few-nanosecond gate speeds and highly parallel in operation, effectively a few hundred MHz. Programmable logic is today's technology for logic learners and implementers. The DPL allows the learner to be more productive and better focus on the underlying logic and integration with the non-logic aspects of non-trivial projects.

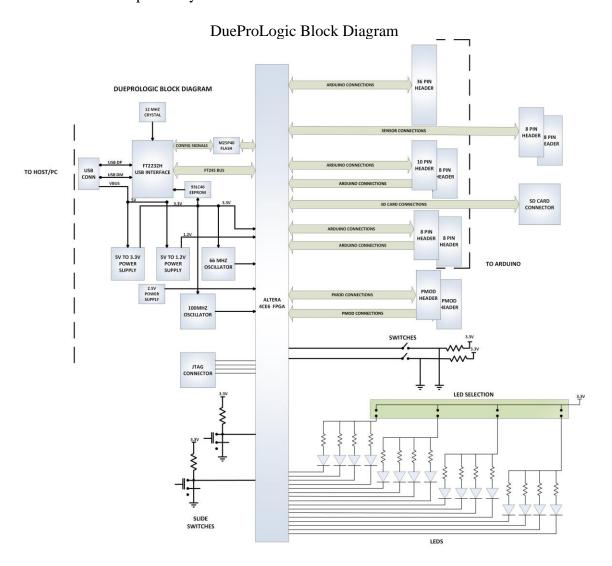

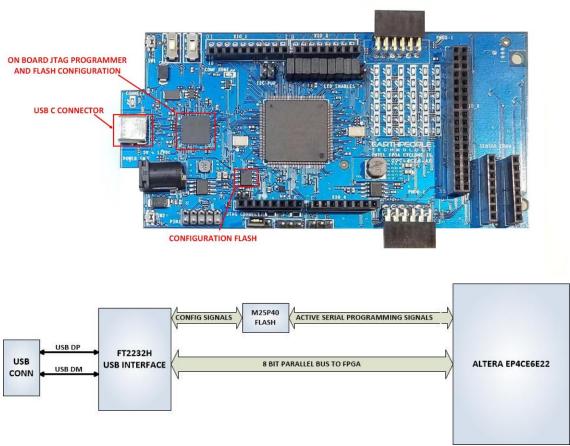

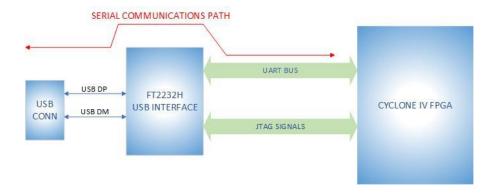

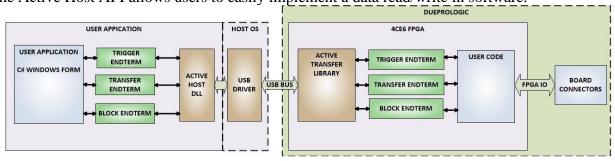

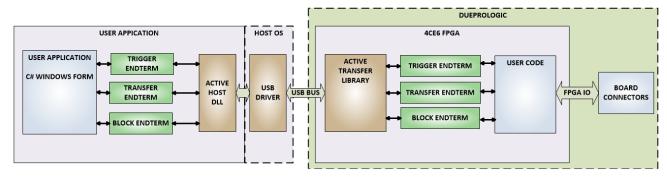

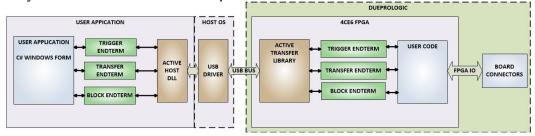

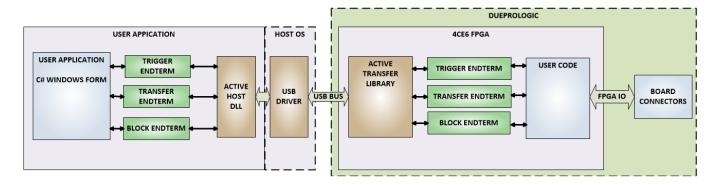

The Earth People Technology FPGA development system hardware consists of a High Speed (480 Mb/s) USB to Serial bus chip and an FPGA. The USB interface provides both Configuration of the FPGA and a Serial transfer path. The software consists of the Active Host SDK for the PC. The firmware includes the Active Transfer Library which is used in the FPGA to provide advanced functions for control and data transfer to/from the Arduino.

The DueProLogic FPGA Development System allows users to write HDL code (either Verilog or VHDL) that will implement any digital logic circuit. The user's HDL code is compiled and synthesized and packaged into a programming file. The programming file is programmed into the Configuration Flash using one channel of the USB to Serial chip, the FT2232H. The Active Host SDK contains COM Port functions which maintains device connection, polling, writes and includes a unique receive mechanism that automatically transfers data from DPL when data is ready. It also alerts the user code when the COM Port has stored the transfer and the data is available to the software GUI (graphical user interface). Users do not need to interface with the USB Host Driver or any Windows drivers. They need only to include the Active Host SDK in their projects. The Active Transfer Libraries must be included in the FPGA project to take advantage of the configurability of the Active Host SDK. All of the drivers, libraries, and project source code are available at www.earthpeopletechnology.com.

# 1.1 Test Driving the Active Host Test Application

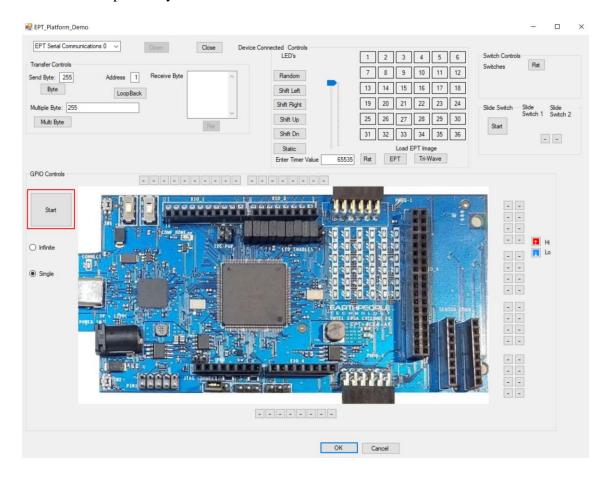

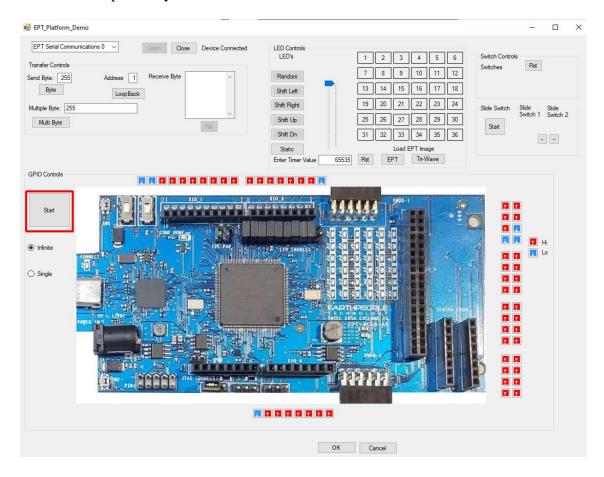

The DueProLogic board comes pre-loaded with the EPT\_Platform\_Demo HDL project in the FPGA. This project allows the user to test out the functions of the Active Host API and the board hardware.

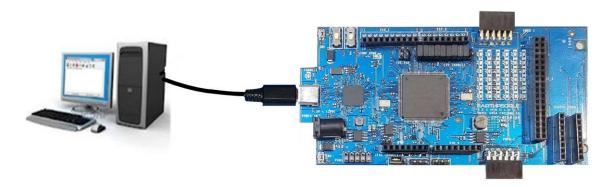

To test drive the application, connect the DPL to the Windows PC using a USB-C cable. Load the driver for the board. See the section "EPT Drivers" for instructions on loading the DPL driver. If the USB driver fails to load, the Windows OS will indicate that no driver was loaded for the device. In the case of the failed USB driver, try rebooting the PC and following the steps in the EPT Drivers section of this User Manual.

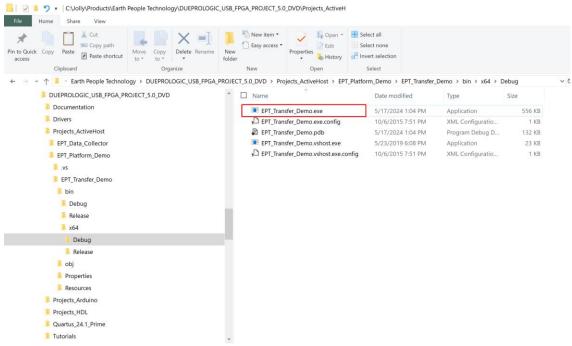

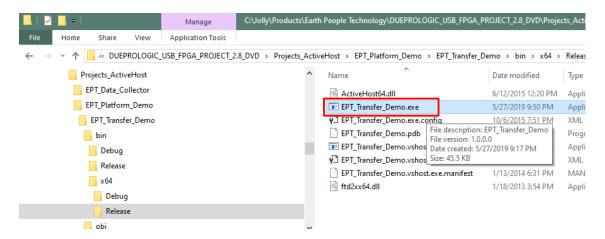

Next, open a Windows Explorer browser.

Browse to the

Projects\_ActiveHost\EPT\_Platform\_Demo\EPT\_Transfer\_Demo\bin\X64\Debug\

#### folder on the DUEPROLOGIC\_USB\_FPGA\_PROJECT\_x.x\_DVD.

Double click on the EPT\_Transfer\_Demo.exe. The application should load with a Windows form.

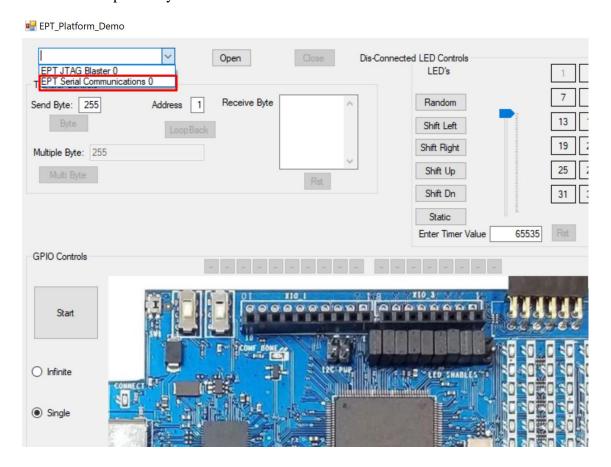

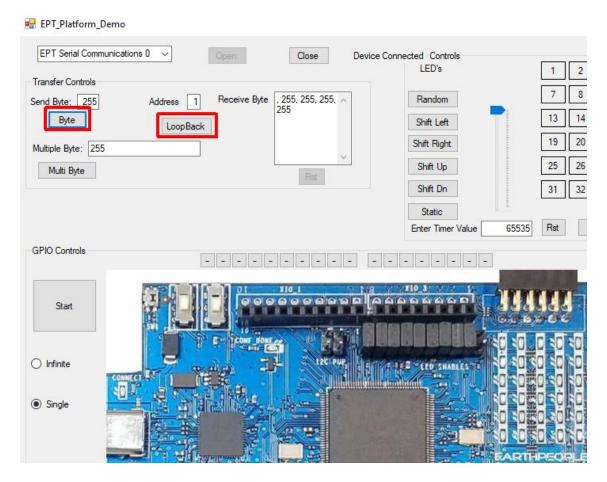

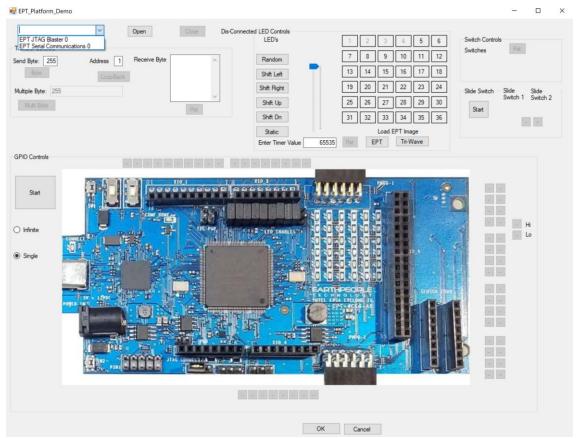

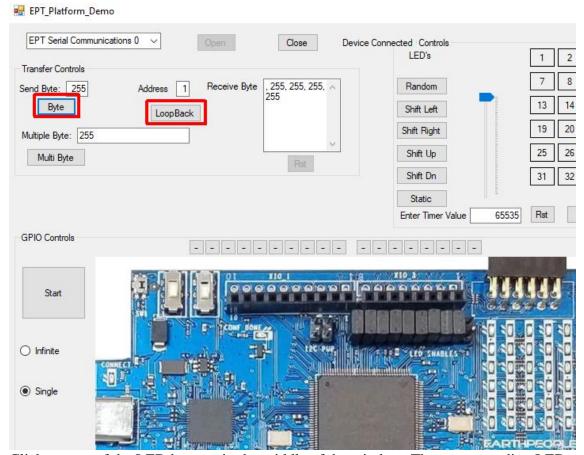

With the application loaded, select the FPGA board (EPT Serial Communications x) from the dropdown combo box and click on the "Open" button.

When the EPT Platform Demo software has properly accessed the board, the "Device Connected" label will appear.

In the "Transfer Controls" Group, leave the Address set at 1 for the Transfer Controls Group.

To exercise the Single Byte Transfer EndTerm, click the "LoopBack" button in the Transfer Controls group. Type in several numbers separated by a space and less 256 into the Multiple Byte textbox. Then hit the Multi Byte button. The numbers appear in the Receive Byte textbox.

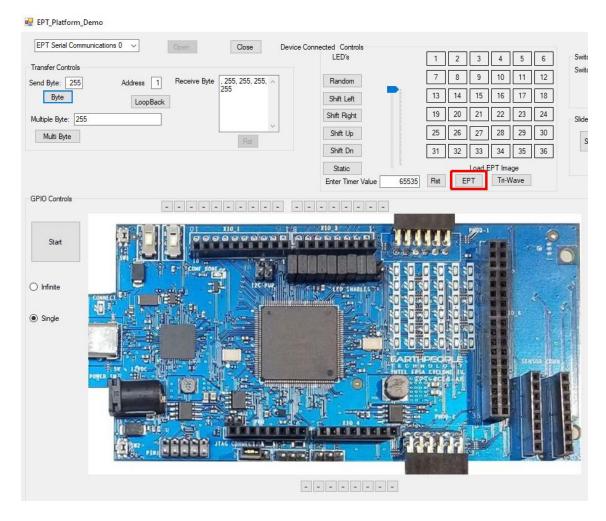

Under LED Controls, press the "EPT" button under the "Load EPT Image".

The characters "EPT" will be displayed on the 6x6 LED array. All the characters cannot be displayed at once, so the "Shift Left" or "Shift Right" button must be pressed to see all characters.

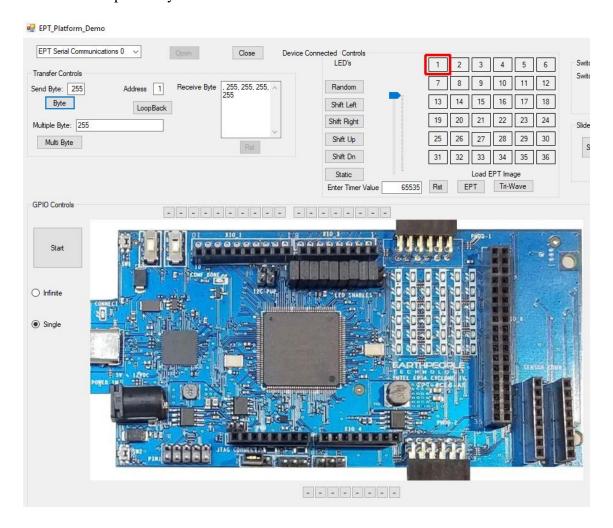

Next press any of the numbered buttons in the "LED Controls" group. This will toggle the corresponding LED in the 6x6 LED Array. It performs this operation as a Block Write. So, an entire LED frame will be transferred to the DueProLogic each time a button is pressed.

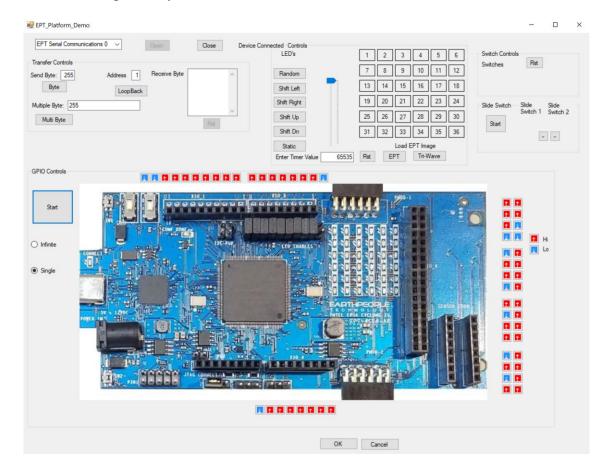

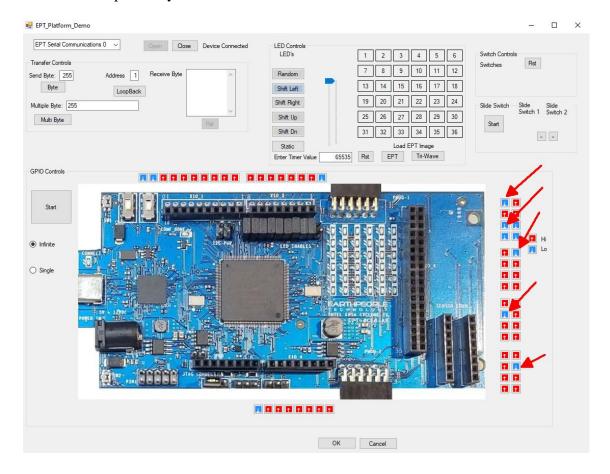

To exercise the Block Transfer EndTerm, click the "Start" button in the GPIO Controls group. The DueProLogic will sample the state of selected Input pins of the FPGA that is connected to a board edge connector. The Transfer Test Window will display the results of each pin, Hi or Lo

The results of each pin are displayed next to the image of the DueProLogic in separate buttons.

Each input at the board edge connector is floating, it has no solid connection to +3.3V or Ground. So, a mixture of Hi and Lo indications is normal.

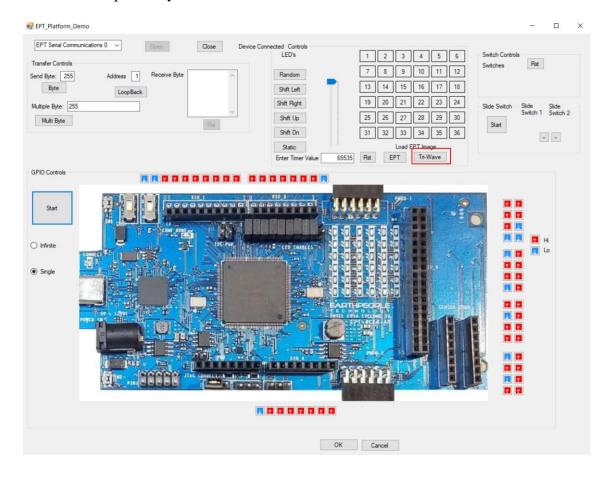

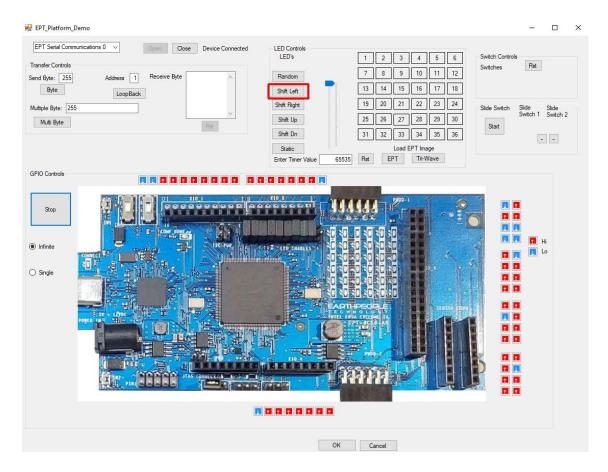

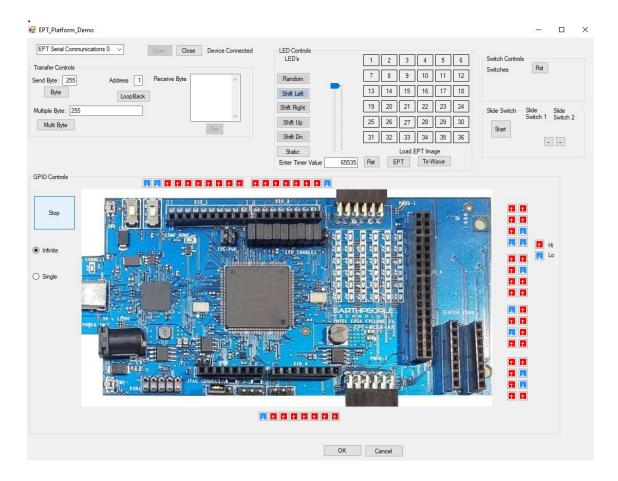

Next, click on the "Tri-Wave" button under the LED Controls Group.

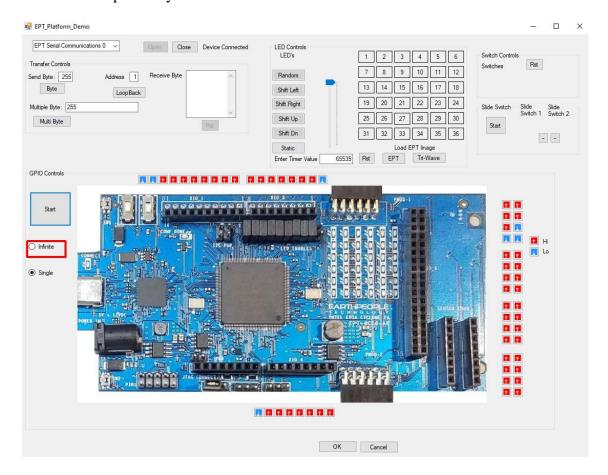

Then, click on the "Infinite" Radio button in the "GPIO Controls" Group Box.

Then, click on the "Start" Button.

Notice that the GPIO's attached to the LEDS in the 6x6 LED Array are now Lo instead of Hi.

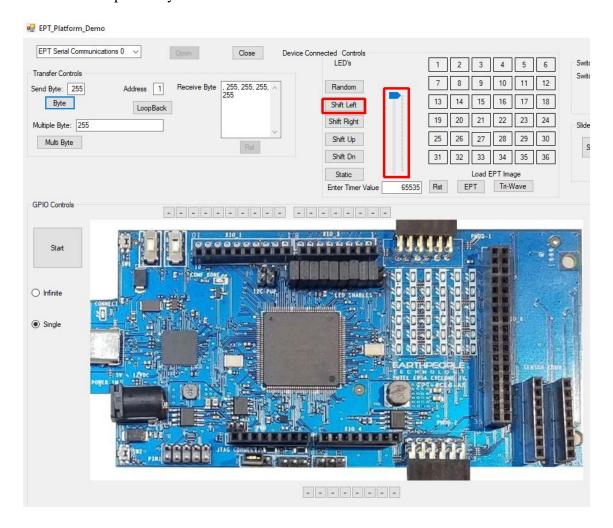

Click on the "Shift Left" button.

Notice the GPIO's connected to the LEDs will change as the image on the 6x6 LED image shifts.

The user can also connect +3.3V or Ground using a jumper to any of the GPIO's in the board edge connector. Be sure NOT to connect +3.3V to a Ground pin or Ground to a +3.3V pin. Consult the Data Sheet for the location of the Inputs on the connectors.

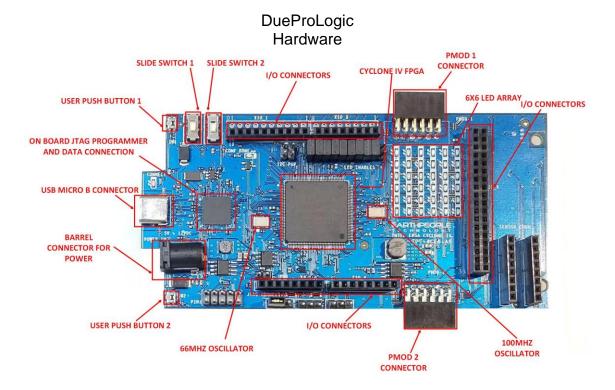

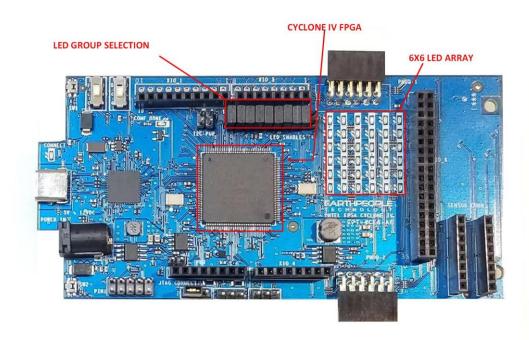

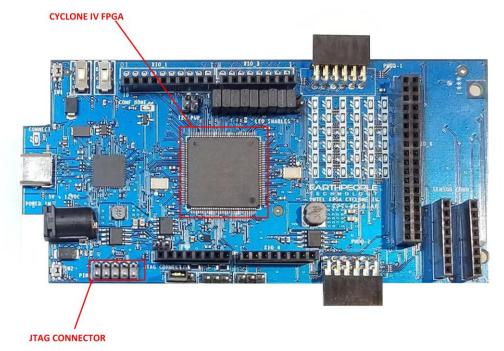

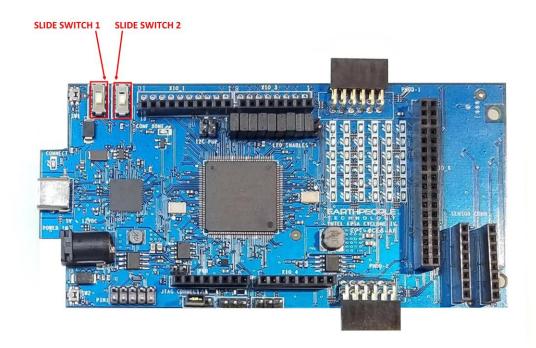

# 1.2 Hardware Description

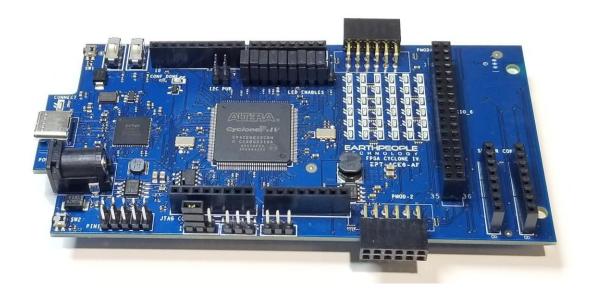

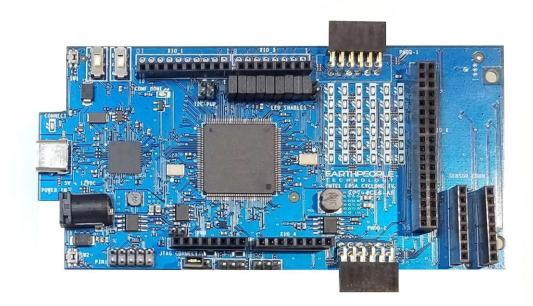

The DueProLogic board is equipped with an Altera EP4CE6E22C8 FPGA; which is programmed using the Altera Quartus Prime software. The FPGA has 6672 Logic Elements and 276480 Total RAM Bits. An on board 66 MHz oscillator is used by the EPT Active Transfer Library to provide serial transfer using the UART method. Fifty Four I/O's from the FPGA are attached to six separate user connectors. The user connectors are organized to fit the Due Arduino platform. There is a separate 36 pin dual row connector at the rear of the board arranged to mate with standard Bread

boards. There are 36 green User LED's, two Slide Switches and two Push Buttons that are controllable by the user code. The hardware features are as follows.

- Altera EP4CE6 FPGA with 6272 Logic Cells

- Dual Channel High Speed USB FT2232H

- 66 MHz oscillator for driving USB data transfers and users code

- 100MHz oscillator for scaling up/down for users needs

- Standard SD Card interface for memory expansion

- 54 user Input/Outputs (+3.3V only)

- 36 Green LED Array accessible by the user

- Two PCB switches accessible by the user

- Two Slide switches

- Two PMOD Connectors

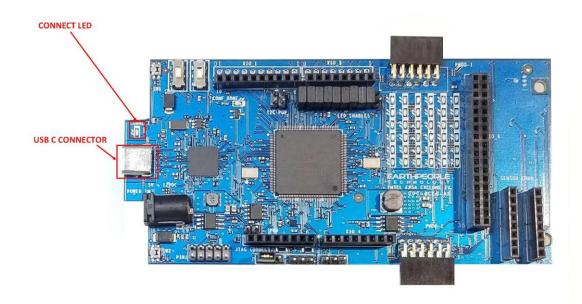

#### 1.2.1 Host PC Connection

The DueProLogic includes an LED that signifies the connection of the board with the Host PC. The connect LED has the word "CONNECT" in silkscreen next to the LED. This LED will only light up once the Host PC has correctly enumerated the USB device (FT2232HQ chip). When this LED is lit up it can tell the user three things:

- Power has been applied to the DueProLogic via USB

- The FT2232HQ chip is working properly

- The Host PC has found the appropriate driver and will communicate with the DueProLogic

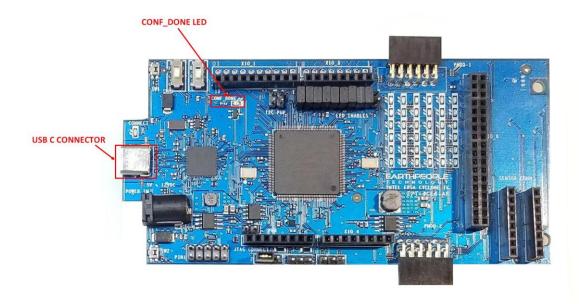

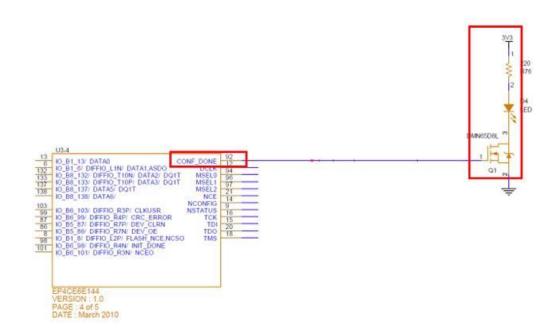

# 1.2.2 CONF DONE LED

The CONF\_DONE LED is connected directly to the FPGA CONF\_DONE signal.

When this LED is lit, it signals to the user that the FPGA has been correctly configured from the configuration flash or the JTAG connection.

# 1.2.3 Jumper Settings

There are six jumper selections on the DPL. These jumper selections will set up the DPL for proper operation and also some optional settings.

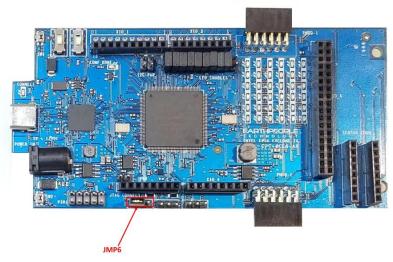

#### 1.2.3.1 JMP6

The jumper setting JMP6 is used for proper operation of configuring the on board flash for the FPGA.

JMP6 is used to allow DCLK to pass from FPGA to the configuration flash. This jumper must have a shunt install on pins 1 and 2 for proper operation of the configuration flash and FPGA.

When using the JTAG only operation of the FPGA (using the \*.sof file to program the FPGA), this jumper should be removed.

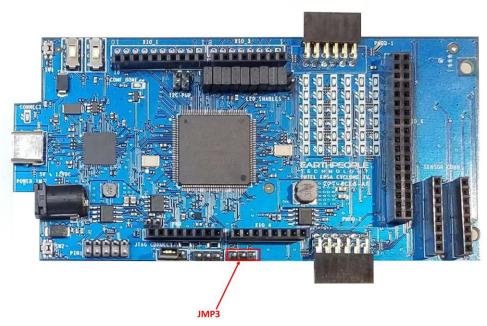

#### 1.2.3.2 JMP3

JMP3 provides a pullup/pulldown to the "NCONFIG" signal of the FPGA. When using the configuration flash to configure the FPGA,

Do Not Add a jumper. When programming the FPGA using JTAG, connect a jumper between pins 1 and 2 to add a pullup to the "NCONFIG" signal.

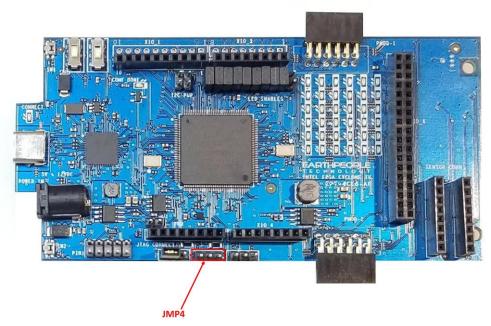

#### 1.2.3.3 JMP4

JMP4 provides a pullup/pulldown to the "CONF\_DONE" signal of the FPGA. When using the configuration flash to configure the FPGA,

Do Not Add a jumper. When programming the FPGA using JTAG, connect a jumper between pins 1 and 2 to add a pullup to the "CONF\_DONE" signal.

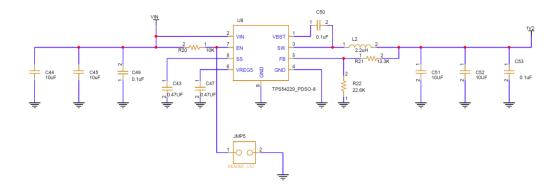

## 1.2.3.4 JMP5

JMP5 provides a pulldown on the EN signal of the 1.2V Power Supply.

FPGA Development System User Manual

This jumper should remain unconnected for proper operation of the FPGA.

Only use this jumper if the configuration flash file has become corrupted and the only method to load a new configuration flash file is to disable the FPGA. For further instructions on the use of this jumper please email Earth People Technology directly.

support@earthpeopletechnology.com

sales@earthpeopletechnology.com

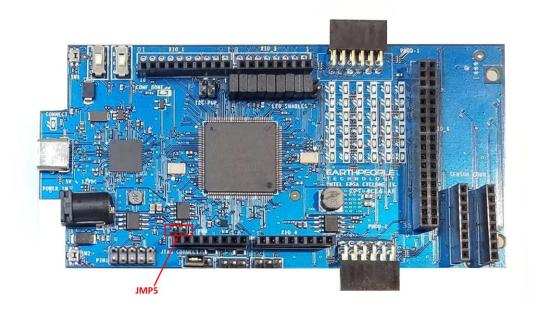

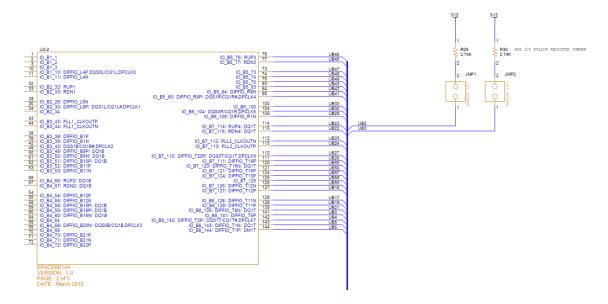

#### 1.2.3.5 JMP1 and JMP2

JMP1 and JMP2 are used to add pullups to the I2C communication signals.

If signals UB2 and UB3 are needed for I2C signals SDA and SDC, connect a shunt to the jumpers to provide the 2.7K Ohm pullup resistors.

#### 1.2.4 Inputs and Outputs

Do not connect a 5Volt device to the DPL

There are 54 Inputs/Outputs which are +3.3Volt only. The FPGA I/O's are organized as separate pins and connect to the Arduino connectors and separate connectors. Each I/O must be defined as input or output in the user code. Each pin of the connectors can behave as either input or output. Refer to the DueProLogic Data Sheet for exact pinout location.

# **DUEPROLOGIC INPUTS OUTPUTS** AT BOARD EDGE HEADERS J11 UB53.....UB22 36 PIN HDR J20 J10 J17 10 PIN 8 PIN HDR HDR J21 J8 8 PIN 8 PIN HDR ALTERA CYCLONE IV FPGA J3 8 PIN 8 PIN UB71.....UB48 HDR PMOD MOD HDR HDR

Each Header includes a Power and Ground connection which allows an easy way to power sensors or bread boards directly from the DPL.

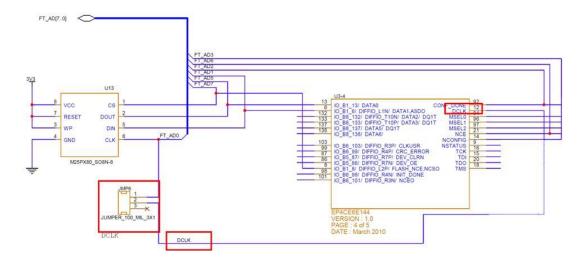

# 1.2.5 FPGA Configuration

The Cyclone IV FPGA is configured for operation when the power is applied to the board. A dedicated Configuration Flash chip is included on the DueProLogic for the purpose of configuring the FPGA on power up. The DPL uses the second channel of the FT2232H chip as a dedicated Flash programming port. The Configuration Flash can be

programmed directly from Quartus Prime by using the EPT-Blaster driver. Follow the instructions in the "EPT Drivers" section of this manual. Follow the instructions in the section "Setting up the Project and Compiling" to program the flash on the DPL.

# 1.2.6 FT2232H Dual Channel USB to Serial Chip

The DueProLogic contains an FTDI 2232H dual channel high speed (480 Mb/s) USB to FIFO (first in-first out) integrated circuit to interface between the Host PC and the FPGA. The FT2232H provides a means of data conversion from USB to serial/parallel data and serial/parallel to USB for data being sent from the FPGA to the PC. Channel A is configured as a Flash Configuration bus and Channel B is configured as a serial bus. FPGA Programming commands are transmitted via the channel A interface. Channel B

has one dual port 4Kbyte FIFO for transmission from Host PC to the FPGA, it also has one dual port 4Kbyte FIFO for receiving data from the FPGA to the Host PC.

The serial communications pathway is used to send and receive data to/from the Host PC. The pathway comprises the USB-C Connector, USB to Serial chip and the Cyclone IV FPGA. The USB driver from FTDI is required for the FT2232H chip. Please see the section "EPT Drivers" for instructions on driver installation.

The serial communications pathway between host and FPGA is transparent to the user. The Active Host API allows users to easily implement a data read/write in software.

Please see the section "Active Host Application" on instructions for how to use the Active Host API to build an application for data read/write between Host and DPL.

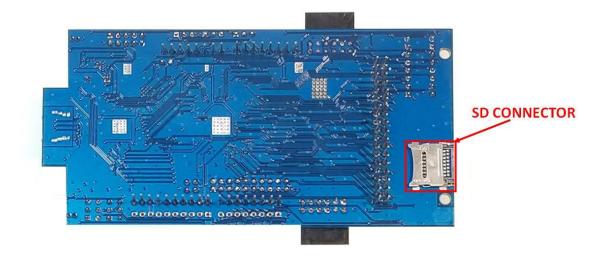

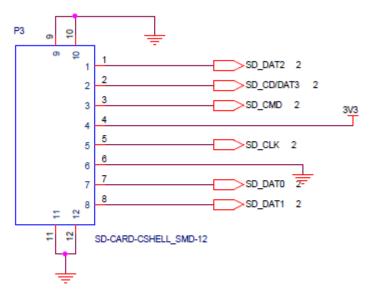

#### 1.2.7 SD Card Interface

The DPL includes a standard SD Card Interface. The SD connector is on the bottom of the DPL. This interface allows the user to add expansion memory or the standard SD interface.

SD Card Connector

#### 1.2.8 SD Card Protocol

There's a ton of information out there on using the MMC/SD SPI protocol to access SD cards but not much on the native protocol. This page hopes to rectify that with information helpful to those implementing a SD host or trying to understand what they're seeing on an oscilloscope.

#### 1.2.8.1 References

- The full MMC Specification is available as JESD84-A44 from the JEDEC website

- The <u>SD Simplified Specification</u> from the SD Card Association covers most of the protocol

- The full SD specification is available after joining the SD Card Association

## 1.2.8.2 Compatibility

MMC, SD, and SDHC cards are broadly compatible at the electrical and framing level. A properly designed controller should be able to handle them all. Some differences are:

- MMC cards are available in both High Voltage (2.7 3.6 V) and Dual Voltage (2.7 - 3.6 and 1.70 - 1.95 V)

- MMC is designed to support multiple cards on the same bus

- During initialisation MMC cards are clocked at 400 kHz or less

- MMC, SD, and SDHC all have different initialisation sequences

#### 1.2.8.3 **Protocol**

The protocol is a strict master/slave arrangement where data is clocked synchronously from the host to the card or from the card to the host over digital lines. Commands are sent from the host to the card and all commands have either no response, a 48 bit response, or a 136 bit response. Some commands may also start a data transfer to or from the card.

There are three types of signal:

- CLK, carrying the clock signal from the host

- CMD, carrying commands from the host and responses from the card

- DAT, carrying data from the host or data from the card

There may be 1, 4, or 8 DAT lines. SD Cards can run at 0 - 25 MHz in Default Mode or 0 to 50 MHz in High-Speed Mode. MMC cards come in different grades that can run at up to 20, 26, or 52 MHz. No matter what all cards start up in 3.3 V, single DAT, and low speed mode with any other features negotiated during the initialisation.

### 1.2.8.4 Physical layer

All communication are at 3.3 V logic levels with 3.3 V being a high and 0 V being a low. CLK comes from the host and idles low. CMD and DAT are bidirectional and idle high. All are driven in a push/pull mode for speed.

Data is clocked into the host or card on the rising edge of CLK and changes on the falling edge. This is equivalent to the SPI (0, 0) mode.

### **1.2.8.5 Framing**

The framing is a bit unusual. It feels like it was written by a embedded software engineer instead of a hardware or protocol engineer as the framing and use of CRCs is unusual and inconsistent. The advantage is that the framing maps through to a software only implementation pretty well.

All transfers start with a zero start bit and finish with a one stop bit. A card may signal that it is still working on the response by keeping the CMD line high until the response is ready.

All commands are 48 bits (6 bytes) long and all responses are either 48 bits (6 bytes) or 136 bits (17 bytes) long. The 48 bit transfers can be thought of as an 8 bit message ID, 32 bit argument, and 8 bit checksum.

Bytes are transferred most significant bit first. Words are transferred most significant byte first.

## 1.2.8.6 Commands and Responses

A command or response has the following format:

| Bit | # | Value                           | Name            |

|-----|---|---------------------------------|-----------------|

| 47  | 1 | 0                               | Start bit       |

| 46  | 1 | 1 for commands, 0 for responses | Transmitter bit |

| 45-40 | 6  |   | Command ID |

|-------|----|---|------------|

| 39-8  | 32 |   | Argument   |

| 7-1   | 7  |   | CRC        |

| 0     | 1  | 1 | Stop bit   |

The CRC is a 7 bit CRC with polynomial  $x^7 + x^3 + 1$ . A table driven form can be found in the Linux kernel under <u>lib/crc7.c</u>. Bitwise forms may be generated using pycrc with the parameters

```

--width=7 --poly=9 --reflect-in=0 --reflect-out=0 --xor-out=0 --xor-in=0 --generate c --algorithm=bit-by-bit-fast such as

```

```

for (int b = 0; b < 8; b++)

{

uint bit = crc & 0x40;

if ((data & 0x80UL) != 0)

{

bit ^= 0x40;

}

data <<= 1;

crc <<= 1;

if (bit != 0)

{

crc ^= 0x09;

}

}</pre>

```

Note that the final CRC must be ANDed with 0x7F.

The CRC seed is zero and is calculated over the start, transmitter, command ID, and argument fields. The resulting CRC is compared for equality with the CRC from the message.

Some examples are:

An APP\_CMD (55) command that prefixes a SD specific command

Bytes: 0x770000000065

#### Fields:

- Start bit = 0

- Transmitter = 1

- Command = 55 (decimal)

- Argument = 00000000

- CRC = 0x32

- Stop bit = 1

The CRC can be generated by feeding 0x77, 0x00, 0x00, 0x00, 0x00 into the CRC function above.

The response to the APP CMD

Bytes: 0x370000012083

Fields:

- Start bit = 0

- Transmitter = 0 (this is a response)

- Response = 55 (decimal)

- Argument = 00000120

- CRC = 0x41

- Stop bit = 1

The response to CMD3 SEND RELATIVE ADDR

Bytes: 0x03B368050019

Fields:

- Start bit = 0

- Transmitter = 0 (this is a response)

- Response = 3 (decimal)

- Argument = 0xB3680500

- CRC = 0x0C

- Stop bit = 1

Note that this cards Relative Card Address (RCA) is 0xB368

#### 1.2.8.7 Data

Data has the following format:

| Bit     | #     | Value | Name      |

|---------|-------|-------|-----------|

| 4113    | 1     | 0     | Start bit |

| 4112-17 | 512*8 |       | Data bits |

| 16-1    | 16    |       | CRC       |

| 0       | 1     | 1     | Stop bit  |

Note that this is for a typical transfer of a block of 512 bytes. The host knows from the command that was sent how many bytes to expect back. There is no other way of knowing the message length.

The CRC is is the ITU-T V.41 16 bit CRC with polynomial 0x1021. A table driven version can be found in the Linux kernel under <a href="lib/crc-itu-t.c">lib/crc-itu-t.c</a>. Note that there is no such thing as 'the' CRC16 so make sure you get the right one. Unlike the commands or responses the CRC is calculated over all of the data bytes and does not include the start bit. The calculated CRC is checked for equality with the received CRC.

PENDING: Add an example data message with CRC.

#### **1.2.8.8** Handover

The CMD and DAT lines are bidirectional. Handover occurs at the end of a command where both the host and the card switch to input mode for two clocks before the card starts driving in push/pull mode. Some commands must be responded to in a fixed number of clocks but most allow an arbitrary time before the response must start.

#### 1.2.8.9 Initialisation

To initialise a SD or SDHC card, send the following:

- Write 74 clocks with CMD and DAT high

- Write CMD0 GO IDLE STATE. This will reset the card.

- Write CMD8 SEND IF COND for 3.3 V parts. If any SDHC cards are

present then you will get a wired-OR response with 0x3F as the command and 0xFF as the CRC and stop bit. Note that this must be sent or SDHC cards will not respond to the following steps

- Write CMD55 APP CMD

- Receive a 55 response

- Write ACMD41 SD SEND OP COND

- Expect a wired-OR response with 0x3F as the command and 0xFF as the CRC and stop bit

- Check the ready bit in the previous response. If the card is not ready then repeat the CMD55/ACMD41 until it is

- Write CMD2 ALL\_SEND\_CID

- Expect a wired-OR response with 0x3F as the command and 0xFF as the CRC and stop bit

- Write CMD3 SEND RELATIVE ADDR

- Expect a 3 response. The upper two bytes of the argument is the

Relative Card Address (RCA) which is used in the next step

- Write CMD7 SELECT CARD with the RCA

- Expect a 7 response

The card is now selected and ready to transfer data. See Figure 4-1 'SD Memory Card State Diagram' in the simplified spec for more information.

See section 4.7.4 'Detailed Command Description' in the simplified spec for more information on the commands and responses.

MMC cards are initialised using a similar but different method.

An example flow captured from Linux on a SC2440 is:

| Phase | Command          | Response     | Notes |

|-------|------------------|--------------|-------|

| CMD0  | 40000000009<br>5 | None         |       |

| CMD55 | 77000000006<br>5 | 370000012083 |       |

| ACMD41<br>SEND_OP_COND         | 69001000005<br>F | 3F00FF8000FF                             | Card is busy            |

|--------------------------------|------------------|------------------------------------------|-------------------------|

| CMD55                          | 77000000006<br>5 | 370000012083                             |                         |

| ACMD41                         | 69001000005<br>F | 3F00FF8000FF                             | Card is still busy      |

| CMD55                          | 77000000006<br>5 | 370000012083                             |                         |

| ACMD41<br>SEND_OP_COND         | 69001000005<br>F | 3F80FF8000FF                             | Card is ready           |

| CMD2 ALL_SEND_CID              | 42000000004<br>D | 3F1D4144534420202010A0400BC10088AD<br>FF |                         |

| CMD3<br>SEND_RELATIVE_ADD<br>R | 43000100007<br>F | 03B368050019                             | RCA<br>of<br>0xB36<br>8 |

Note the missing CMD8 as this controller does not support SDHC. I didn't capture the final CMD7.

# **1.2.8.10** Reading

Once initialised reading from a card is straight forward.

To read a single page:

- Send CMD17 READ\_SINGLE\_BLOCK with the offset to read from as the argument

- Receive on the DAT lines

- Send CMD12 STOP\_TRANSMISSION once the block has been received To read consecutive pages:

- Send CMD18 READ\_MULTIPLE\_BLOCK with the starting offset as the argument

- Receive as many blocks as you want on the DAT lines

- Send CMD12 STOP\_TRANSMISSION once the done

Note that there will be a response to these commands and the response may be interleaved with the data. See Figure 3-3: (Multiple) Block Read Operation for more information.

On SDHC cards the offset is in terms of 512 byte blocks. On SD cards the offset is in bytes and the number of bytes received depends on CMD16 SET BLOCKLEN

#### 1.2.9 LEDs

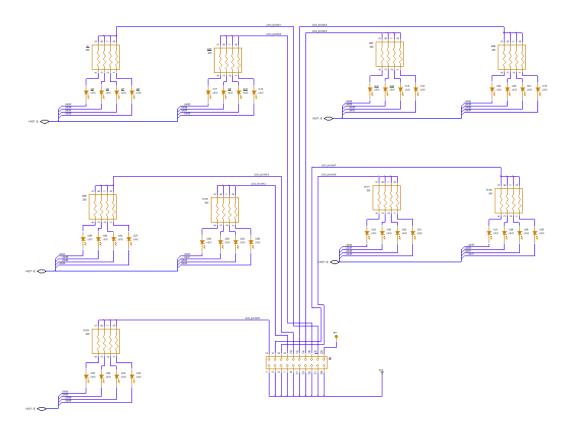

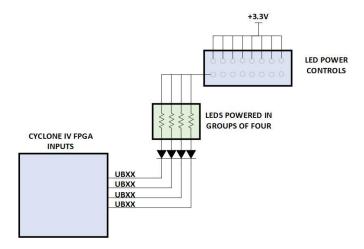

The DueProLogic includes a 6x6 Green LED array. Each LED is sinked to an individual pin on the FPGA. Each LED is current limited to 6mA. The total current consumed for all 36 LEDs is 216mAs. The FPGA can easily sink this current. So, individually sinking all 36 LEDs makes easy control for User Code. The DueProLogic also contains a method to turn on/off the LEDs in four unit blocks. A jumper is used to control the state of each LED block.

LED Power Control allows a group of four LEDs to be powered by one jumper. When the jumper is connected, the LEDs are powered by +3.3V. When disconnected, the LEDs will not light up and the IO pin in the appropriate Board Edge Connector can be used without an LED.

FPGA Development System User Manual

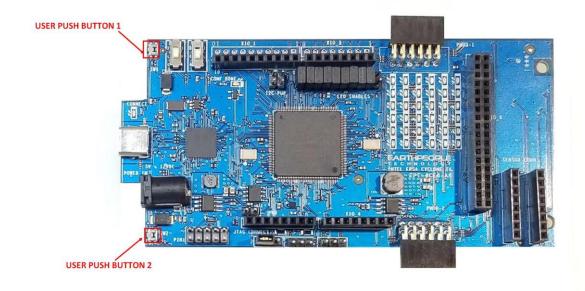

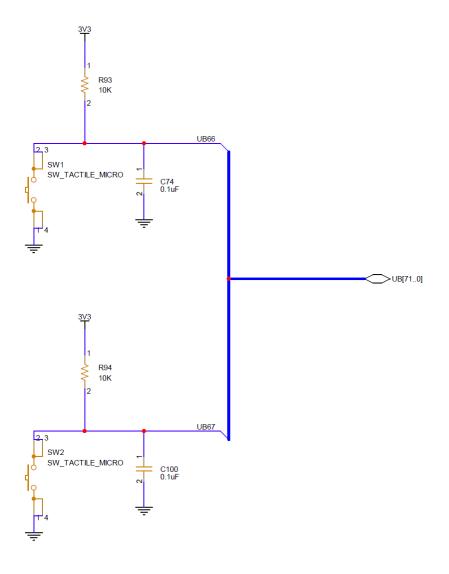

## 1.2.10 Pushbuttons

The DueProLogic includes two pushbuttons that can be used in a way the user would like. They are both attached to separate debounce circuits. These pushbuttons were designed to use as little PCB are as possible. The switch is engaged by the plunger which is directed off the PCB.

The switches will momentarily provide a ground connection to the appropriate pin on the FPGA. When Idle, the signals are pulled high through a 10K Ohm resistor.

Push Button Switches

| Component | Net Name | Pin on Cyclone IV |

|-----------|----------|-------------------|

| SW1       | UB66     | 91                |

| SW2       | UB67     | 90                |

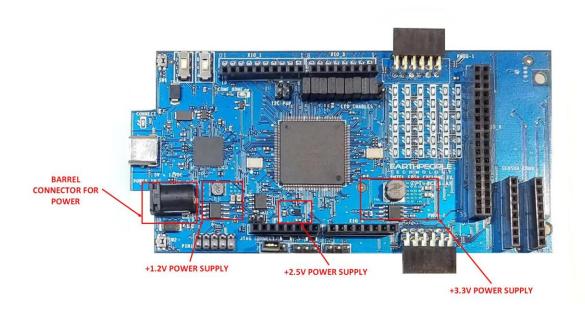

## 1.2.11 Power Options

There are two power options for the DueProLogic

- USB-C Connection to a PC (+5VDC)

- Barrel Connector (+5VDC to +12VDC)

The USB Micro B Connector is a the standard connector specified by the USB SIG.

The Barrel Connector is the located on the front of the board. It has 2.0mm inner diameter and 5.5mm outer diameter. The inner male connection is the positive connection and the outer connection is the ground. This connection can accept between +5VDC and +12VDC power. However, great care must be used when using this connection. This power is applied to several pins on the I/O headers. Consult the Data Sheet for these connections.

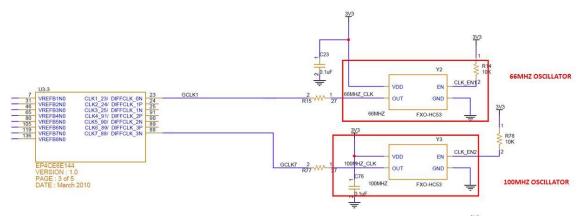

#### 1.2.12 Clock Domains

There are two clock domains external to the Cyclone IV FPGA, 66 MHz and 100 MHz. The 66 MHz oscillator is a  $\pm 3.3$ VDC device that provides a high speed clock to the FPGA. It is a CMOS device that provides a stable 66 MHz at  $\pm 50$  ppm. This clock can be used directly in the user code or use it as an input to one of the PLL's internal to the FPGA. It is intended that this clock will drive the logic of the user code. If a different

clock frequency is required in the user code, use the PLL scale up/down to produce the desired clocking.

The 100MHz oscillator is a +3.3VDC device that provides a stable source for high speed clocking. This oscillator can be used for higher speed functions such as fast communications, memories and control.

Both oscillators have an enable signal that are individually controlled by the FPGA. The oscillators are operational when the enable signal is high. The oscillators enable signals each have 10K pullups to keep them on at all times.

| Component              | Signal Name | FPGA Pin |

|------------------------|-------------|----------|

| Y2 (66MHz Oscillator)  | 66MHZ_CLK   | 23       |

| Y3 (100MHz Oscillator) | 100MHZ_CLK  | 88       |

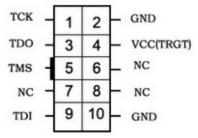

## 1.2.13 JTAG Header

The DueProLogic can be programmed by writing to the on board configuration flash or by directly accessing the FPGA JTAG connection.

Connector J13 provides access to the FPGA JTAG connections. The pinout follows the USB Blaster arrangement which is standard on all Intel/Altera devices. Be sure to follow the pin 1 orientation.

This connector uses the standard Altera Blaster connector pinout.

The VCC(TRGT) is set to +3.3V on the DueProLogic. There are no jumper settings to make in order to program the Cyclone IV FPGA. Just connect a compatible Blaster to the connector and the PC, then use the Quartus software to program the FPGA.

Connect an Intel/Altera compatible programmer to J13, and the FPGA can be programmed directly from Quartus Prime Lite.

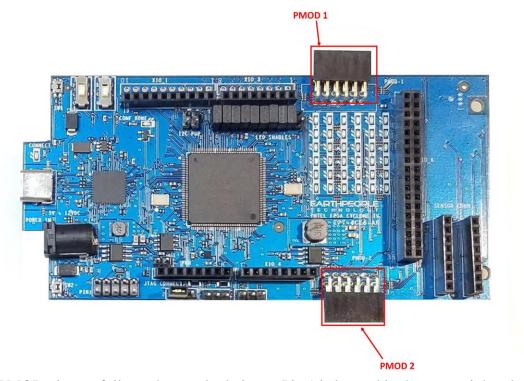

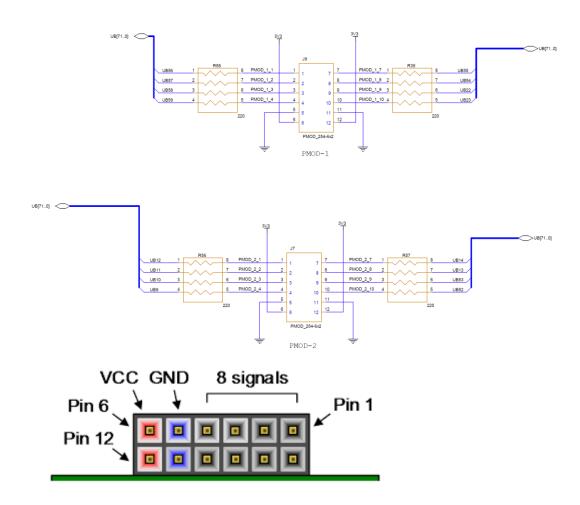

### 1.2.14 PMOD Connectors

The DueProLogic includes two PMOD Connectors. These two connectors are located towards the rear of the board.

The PMOD pinouts follows the standard pinout. Pin 1 is located in the upper right when facing the connector.

VCC is +3.3V and the Inputs and Outputs of the 8 signals are +3.3V only. The eight I/O's are connected directly to FPGA pins and can be designated as any communications standard.

The PMOD have the following connections to the Cyclone IV chip:

| PMOD Pin Number | Signal Name | Cyclone IV Pin Number |

|-----------------|-------------|-----------------------|

|                 |             |                       |

| 1-1             | UB56        | 121                   |

| 1-2             | UB57        | 124                   |

| 1-3             | UB58        | 125                   |

| 1-4             | UB59        | 126                   |

| 1-7             | UB55        | 120                   |

| 1-8             | UB54        | 119                   |

| 1-9             | UB22        | 115                   |

| 1-10            | UB23        | 114                   |

| 2-1             | UB12        | 67                    |

| 2-2             | UB11        | 66                    |

| 2-3             | UB10        | 53                    |

| 2-4             | UB9         | 52                    |

| 2-7             | UB14        | 55                    |

| 2-8             | UB13        | 54                    |

| 2-9             | UB53        | 69                    |

| 2-10            | UB52        | 70                    |

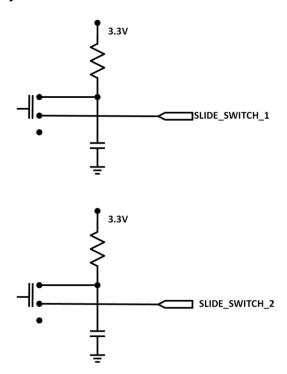

#### 1.2.15 Slide Switches

The DueProLogic includes two slide switches. Both are full contact switches. They include a 1uF cap to ground to debounce both switches.

The slide switches provide a connection to either +3.3V in position 1 or Ground in position 2.

| Component | Net Name       | Pin on Cyclone IV |

|-----------|----------------|-------------------|

| SW3       | SLIDE_SWITCH_1 | 91                |

| SW4       | SLIDE_SWITCH_2 | 90                |

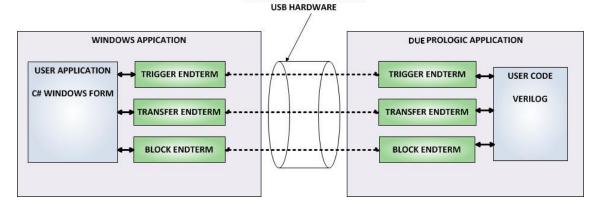

# 1.3 FPGA Active Host Development

The DueProLogic comes complete with step by step instructions on building an entire communications system from FPGA to Windows Host. Using the EPT Active Host SDK provides an easy to use programming interface. The tools required are the free Visual Studio IDE and the free Quartus Prime.

The DueProLogic also comes with instructions on how to build a communications systems between the Arduino Due and the DPL. The DVD included in the kit has all source files, compiled projects and user manuals to assist the user in using the software. In order to assemble a full communications system between the PC and the DPL, the following software items are required:

- Active Host SDK This library provides the communication mechanism on the PC

- Active Transfer library This library is included and synthesized into the users code on the FPGA

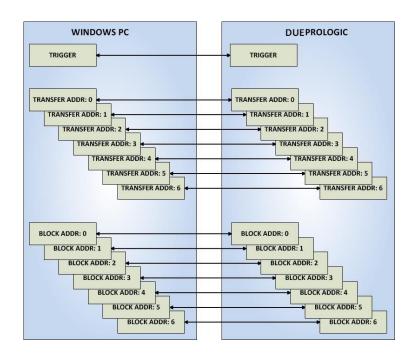

These two software components provide a communication mechanism by talking to each other over an item called "EndTerms". EndTerms is the name given to the virtual "pipes" provided by the above libraries. The next two sections provides a brief introduction to EndTerms. Following sections will provide greater detail on using EndTerms.

#### 1.4 Active Host EndTerms

The Active Host SDK is provided as a set of functions, including the COM Port functionality, which easily interfaces to application software written in C#, C++ or C. It runs on the PC and provides transparent connection

VIRTUAL PIPES THROUGH THE

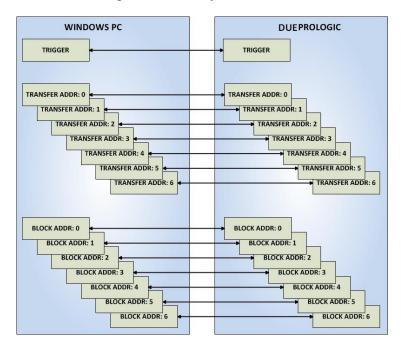

from PC/Windows application code through the USB driver to the user FPGA code. The user code connects to "Endterms" in the Active Host SDK. These Host "Endterms" have complementary HDL "Endterms" in the Active Transfer Library. Users have seamless bi-directional communications at their disposal in the form of:

- Trigger Endterm

- Transfer Endterm

- Block Endterm

User code writes to the Endterms as function calls. Just include the address of the individual module (there are eight individually addressable modules of each Endterm).

Immediately after writing to the selected Endterm, the value is received at the HDL Endterm in the FPGA.

```

BlockTransferPayload.cs

Form1.cs 🗢 × Form1.cs [Design

EPT_Transfer_Demo

Form1.Designer.cs

C# EPT_Transfer_Demo

▼ EPT_Transfer_Demo.EPT_Transfer_Demo

509

510

511

private void btnCountUp_Click(object sender, EventArgs e)

512

513

LoadTimerValue();

514

515

//Send the Inital value to the Active Transfer Module 2

516

//for loading into the Shift Left LED

517

EPT_AH_SendByte(0x01, (char)LEDStatus);

518

//Send Trigger 1 to latch the Shift-Count Value

519

520

EPT_AH_SendTrigger((byte)0x02);

521

//Send the start Shift Right to the Control Register

522

EPT_AH_SendTransferControlByte((char)2, (char)0x40);

523

524

525

//Set the Button State so User can know which function is selected

SetLEDControlButtons(SELECT_COUNT_UP);

526

527

}

528

529

private void btnCountDown Click(object sender, EventArgs e)

530

100 %

```

The above is a code sample from a C# Windows Form. You can see functions that write a byte to the FPGA (EPT\_AH\_SendByte(0x01, (char)LEDStatus)) and write a trigger bit to the FPGA (EPT\_AH\_SendTrigger((byte)0x02).

```

954

955

ACTIVE TRIGGER INST

active_trigger

956

957

.uc clk

(CLK 66),

958

.uc reset

(RST),

959

.uc in

(UC IN),

960

(uc out m[ 0*22 +: 22 ]),

.uc_out

961

962

.trigger to host

(trigger out),

.trigger_to_device

963

(trigger in byte)

964

965

966

967

active_transfer

ACTIVE TRANSFER INST 1

968

969

.uc clk

(CLK 66),

970

.uc reset

(RST),

971

.uc in

(UC IN),

972

.uc out

(uc out m[ 1*22 +: 22 ]),

973

974

.start transfer

(led start transfer),

975

.transfer received

(led transfer in received),

976

977

.transfer busy

(),

978

979

.uc addr

(3'h1),

980

981

.transfer to host

(led_host_transfer_byte),

.transfer_to_device

982

(led device transfer byte)

983

```

The above code is the interface Verilog which resides in the FPGA. When the C# Windows form sends a byte or trigger, the signals in the FPGA code react and allow the user code to receive the byte and trigger and perform some function with the information. In the case of this example, the LEDs will change state.

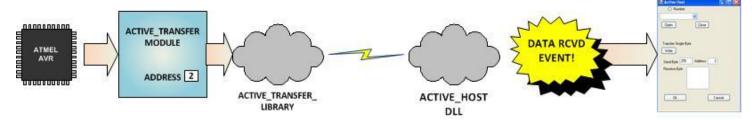

Receiving data from the FPGA is made simple by Active Host. Active Host transfers data from the FPGA as soon as it is available. It stores the transferred data into circular buffer. When the transfer is complete, Active Host invokes a callback function which is registered in the users application. This callback function provides a mechanism to transparently receive data from the FPGA. The user application does not need to schedule a read from the USB or call any blocking threads.

# 1.5 Active Transfer EndTerms

The Active Transfer Library is a portfolio of HDL modules that provides an easy to use yet powerful USB transfer mechanism. The user HDL code communicates with EndTerms in the form of modules. These EndTerm modules are commensurate with the Active Host EndTerms. There are three types of EndTerms in the Active Transfer Library:

- Trigger Endterm

- Transfer Endterm

- Block Endterm

They each have a simple interface that the user HDL code can use to send or receive data across the USB. Writing to an EndTerm will cause the data to immediately arrive

at the commensurate EndTerm in the Active Host/user application. The transfer through the USB is transparent. User HDL code doesn't need to set up Endpoints or respond to Host initiated data requests. The whole process is easy yet powerful.

### 2 EPT Drivers

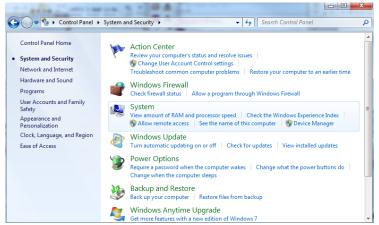

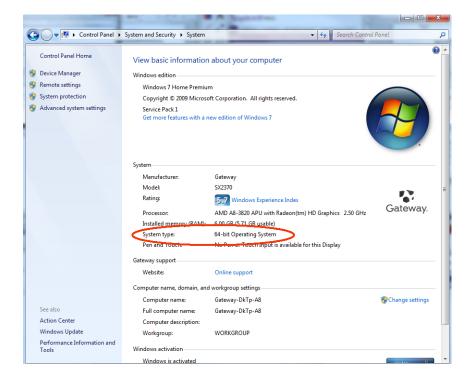

The DueProLogic Development system requires drivers for any interaction between PC and the board. The communication between the two consists of programming the FPGA and data transfer. In both cases, the USB Driver is required. This will allow Windows to recognize the USB Chip and setup a pathway for Windows to communicate with the USB hardware.

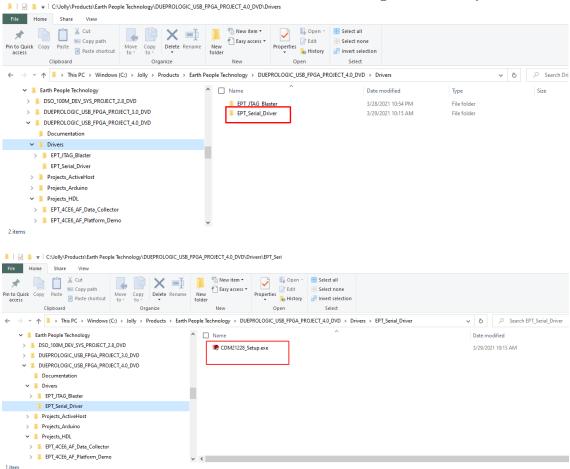

#### 2.1 USB Driver

The DueProLogic uses an FTDI FT2232H USB to Serial chip. This chip provides the USB interface to the PC and the serial/FIFO interface to the FPGA. The FT2232H requires the use of the FTDI USB driver. To install the driver onto your PC, use the EPT\_Serial\_Driver Folder. The installation of the FTDI 2.12.28 driver is easily accomplished by double clicking the CDM21228\_Setup.exe.

Locate the EPT\_Serial\_Driver folder in the Drivers folder of the DUEPROLOGIC\_USB\_FPGA\_PROJECT\_x.x\_DVD using Windows Explorer.

Double click on the \*.exe file and select the default settings when the software tool queries the user.

Plug in the DueProLogic into an available USB port.

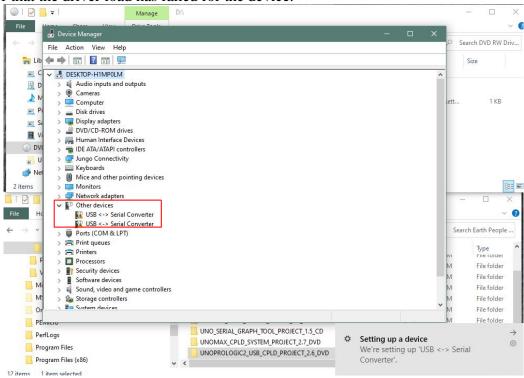

Windows will attempt to locate a driver for the USB device. Allow Windows to install the driver for the DueProLogic.

If Windows cannot load a driver for the DPL, a notification window will inform the user that the driver load has failed for the device.

Right click on the "USB <-> Serial Converter" icon that failed to load. Then select the "Load driver from Known Location". Navigate to the DUEPROLOGIC\_USB\_FPGA\_PROJECT\_x.x\_DVD/drivers/EPT\_Serial\_Driver folder. Allow the Windows PC to locate and install the driver.

If this method continues to fail, contact support at Earth People Technology using the following methods:

www.earthpeopletechnology.com/Forums support@earthpeopletechnology.com sales@earthpeopletechnology.com

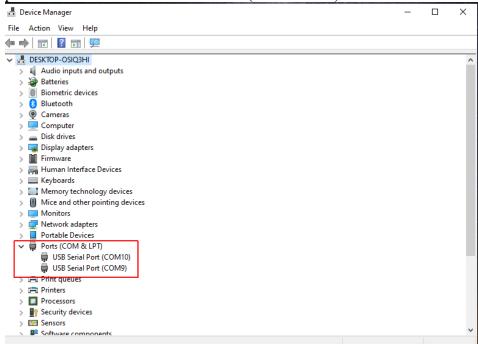

If the driver is successfully installed, Windows will inform the user. The user can check Device Manager to ensure the correct driver was installed for the DPL. The DPL will show up as two COM Ports under the "Ports (COM &LPT)" under the Device Manager.

When this is complete, the drivers are installed and the DueProLogic can be used for programming and USB data transfers.

# 2.2 JTAG DLL Insert to Quartus Prime Lite

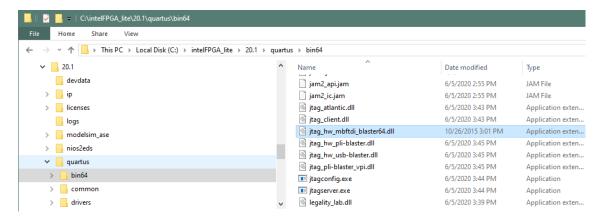

The JTAG DLL Insert to Quartus Prime Lite allows the Programmer Tool under Quartus to recognize the DueProLogic. The DueProLogic can then be selected and perform programming of the FPGA. The file, jtag\_hw\_mbftdi\_blaster.dll must be placed into the folder that hosts the jtag\_server for Quartus.

## 2.2.1 Installing Quartus

You must install Quartus Prime to configure the DueProLogic. Altera Quartus Prime must be downloaded from the Altera website.

Download the Quartus Prime by following the directions in the Section Downloading Quartus.

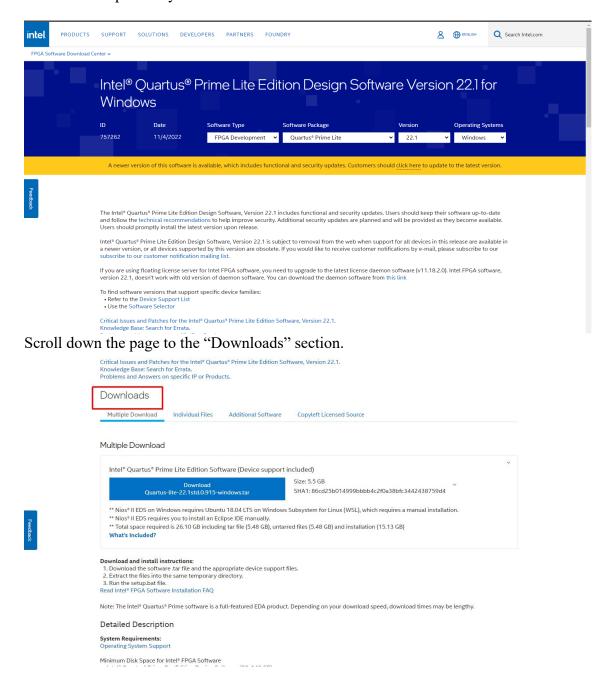

## 2.2.2 Downloading Quartus

The first thing to do in order build a project in Quartus is to download and install the application. You can find the latest version of Quartus at:

### Intel FPGA Quartus Prime Lite

\*\*Please be advised, Intel is prone to changing their website graphics every few months. The guide below is several months out of date. Please follow the latest instructions on the Quartus Prime Lite Download website. The instructions here are only meant as a guide to getting the software downloaded.\*\*

You will first need to apply for an account with Intel. Then use your login and password to access the download site. Click on the Download Windows Version.

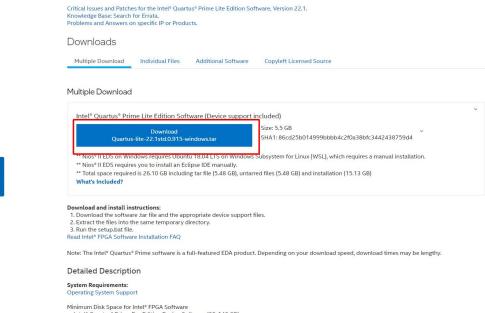

Click on the "Download Quartus-lite-22.1 xxxxxx Windows Tar.

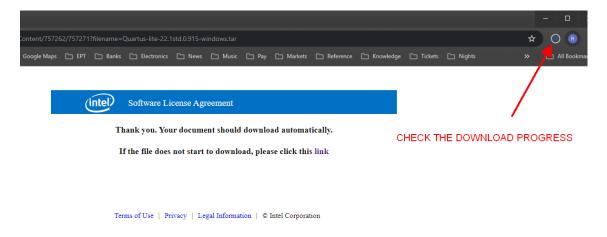

Click through the Legal Stuff.

Software License Agreement

#### Legal Disclaimer

PLEASE NOTE: This version of software ("Software") does not contain the latest functional and security updates. In order to use this version, you must first acknowledge the following term, which supplements and supersedes any inconsistent provision in the version of the Intel® FPGA Software License Subscription Agreement for the product (e.g., Intel® Quartus® Prime Software, Intel® HLS Compiler, Intel® FPGA SDK for OpenCL™, DSP Builder for Intel® FPGAs, or Advanced Link Analyzer) with which you use the Software:

Intel does not give or enter into any condition, warranty, or other term:

- with respect to any malfunctions or other errors in its Software caused by virus, infection, worm or similar malicious code not developed or introduced by Intel; or

- ii. to the effect that any Software will protect against all possible security threats, including intentional misconduct by third parties. Intel is not liable for any downtime or service interruption, for any lost or stolen data or systems, or for any other damages arising out of or relating to any such actions or intrusions or resulting from use of Software. Intel does not give or enter into any condition, warranty, or other term with respect to interoperability.

Intel does not warrant or assume responsibility for the accuracy or completeness of any information, text, graphics, links or other items within the Software. Please click "Accept" below to continue the download process.

Reject

Terms of Use | Privacy | Legal Information | © Intel Corporation

This will start the download.

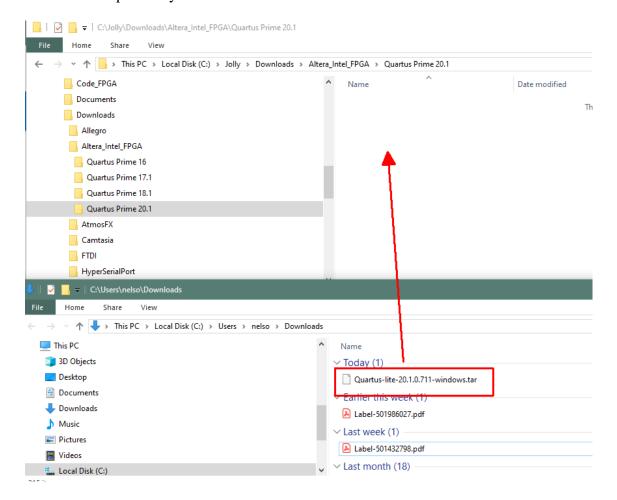

The file is 13.9 GB (or greater), so this could take a couple of hours depending on your internet connection. When download is complete, store the \*.tar file in a directory on your PC.

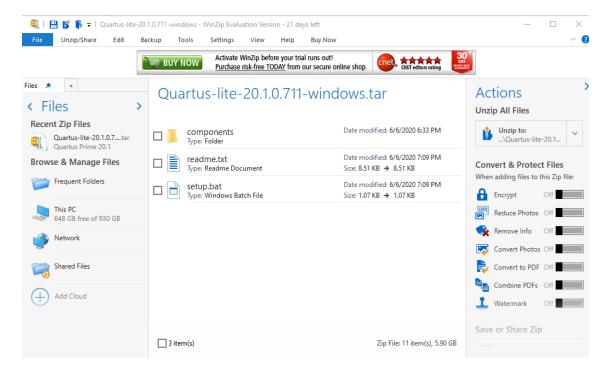

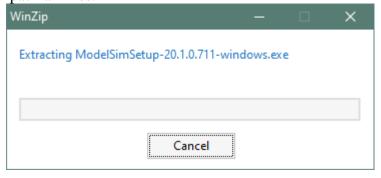

Use a tool such as WinZip to Extract the \*.tar file.

The tool will unpack all files.

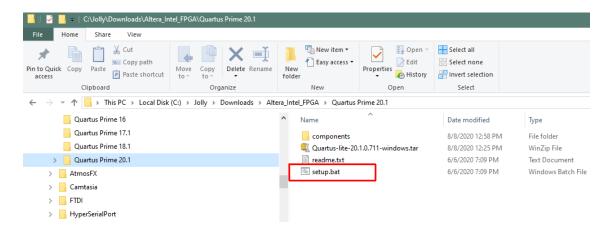

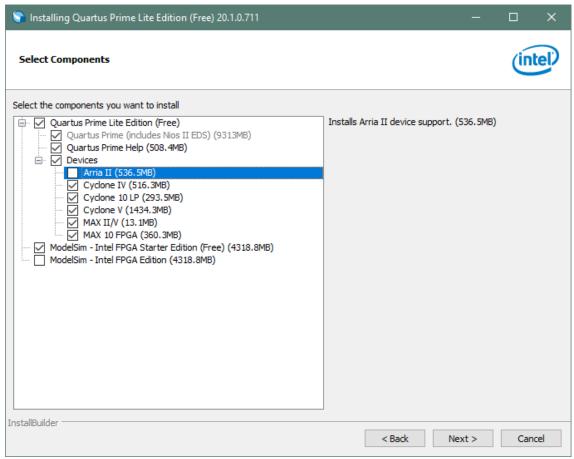

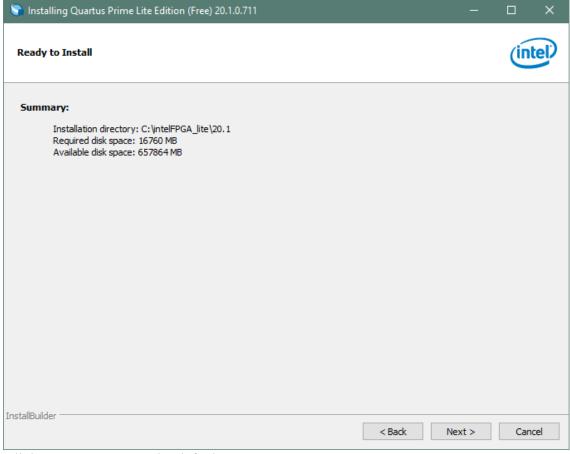

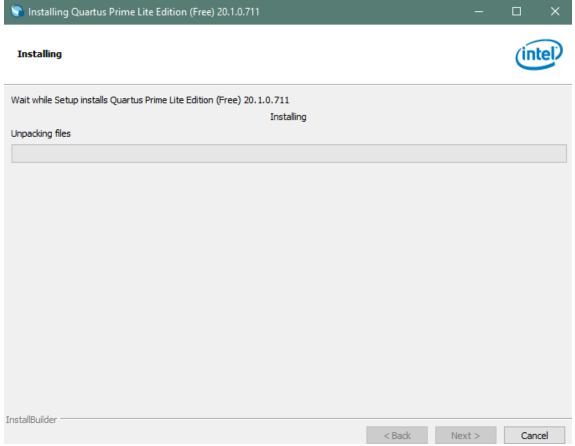

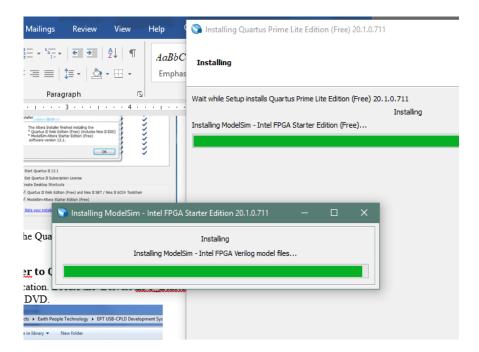

# 2.2.3 Quartus Installer

When the unpacking finishes from the previous section, double click the setup.bat file in the download folder.

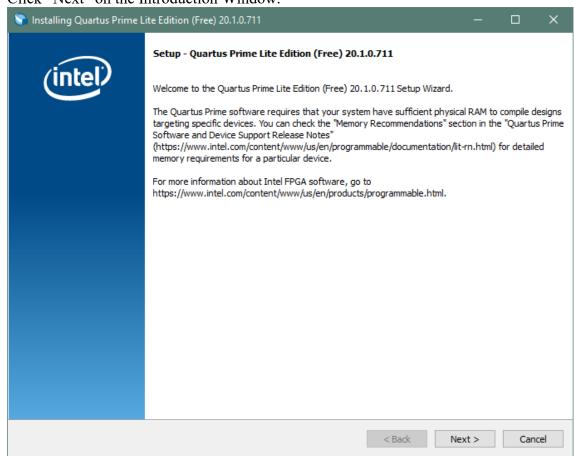

#### Click "Next" on the Introduction Window.

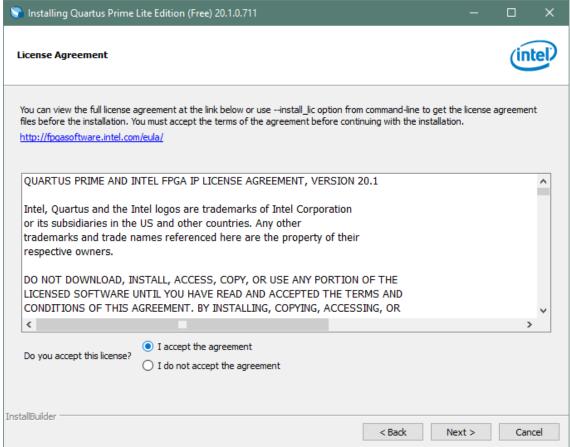

Click the checkbox to agree to the license terms. Then click "Next".

Click "Next" and accept the defaults.

At the Select Products Window, de-select the Quartus Prime Supbscription Edition by clicking on its check box so that the box is not checked. Then click on the check box by the Quartus Prime Web Edition (Free).

Click "Next" to accept the defaults

Click "Next" to accept the defaults

Wait for the installation to complete.

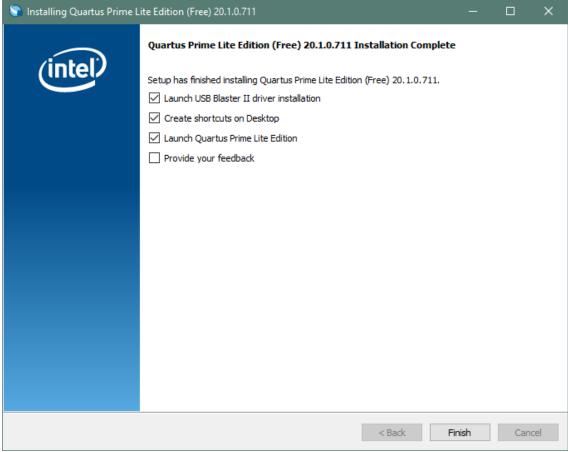

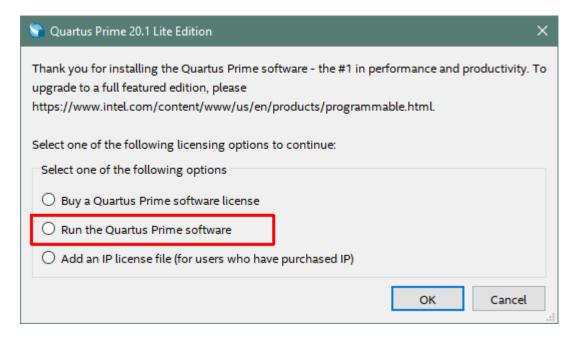

Click "Ok", then click "Finish". The Quartus Prime is now installed and ready to be used.

# 2.2.4 Adding the EPT\_Blaster to Quartus Prime

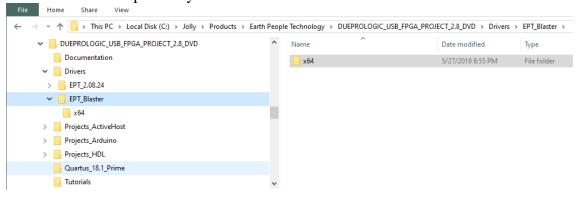

Close out the Quartus Prime application. Locate the \Drivers\EPT\_Blaster folder on the EPT\_FPGA Development System DVD.

#### Follow these directions:

- 1. Open the C:\EPT FPGA Development System DVD\Drivers\EPT\_Blaster\x64 folder.

- 2. Select the file "jtag\_hw\_mbftdi\_blaster.dll" and copy it.

- 3. Browse over to C:\intelFPGA\_lite\xx.x\quartus\bin64.

- 4. Right click in the folder and select Paste

- 5. Click Ok.

- 6. Open the Quartus Prime application.

The DLL is installed and the JTAG server should recognize it. Go to the section "Programming the FPGA" of this manual for testing of the programming. If the driver is not found in the Programmer Tool->Hardware Setup box, contact Earth People Technology for support. There are three methods to contact EPT for support:

https://www.earthpeopletechnology.com->Forums support@earthpeopletechnology.com sales@earthpeopletechnology.com

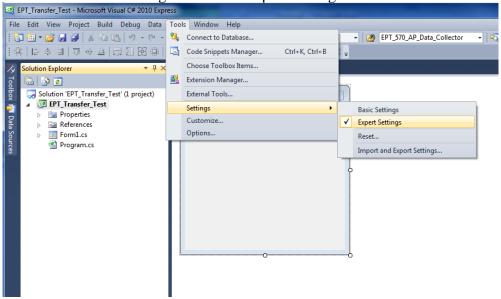

# 2.3 Active Host Application SDK

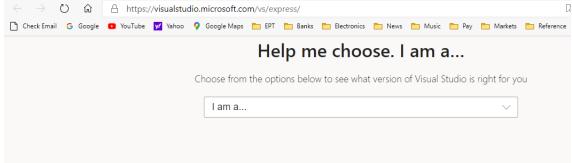

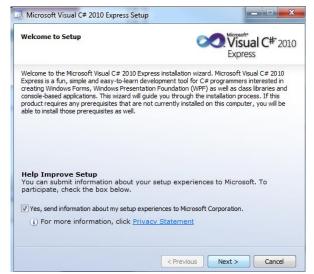

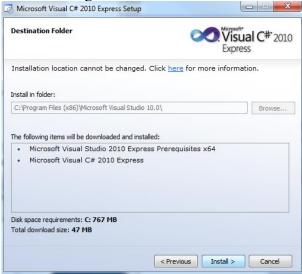

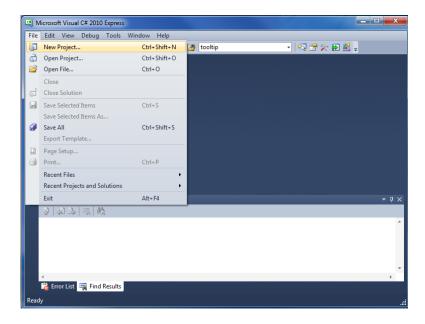

Download the latest version of Microsoft Visual C# Express environment from Microsoft. It's a free download.

https://visualstudio.microsoft.com/vs/express/

Go to the website and click on the "+" icon next to the Visual C# Express.

# Click on the "Express 20xx for Windows Desktop" hypertext.

# Still want Visual Studio Express?

**Express 2017 for Windows Desktop**

Supports building managed and native desktop applications.\*

#### **Express 2015 for Windows Desktop**

Supports the creation of desktop applications for Windows.

The download manager file will download the "WDExpress.exe" file.

# Still want Visual Studio Express?

**Express 2017 for Windows Desktop**

Supports building managed and native desktop applications.\*

#### **Express 2015 for Windows Desktop**

Supports the creation of desktop applications for Windows.

### Express 2015 for Web

Create standards-based, responsive websites, web APIs, or real-time online experiences using ASP.NET.

#### Express 2015 for Windows 10

Provides the core tools for building compelling, innovative apps for Universal Windows Platform. Windows is required.

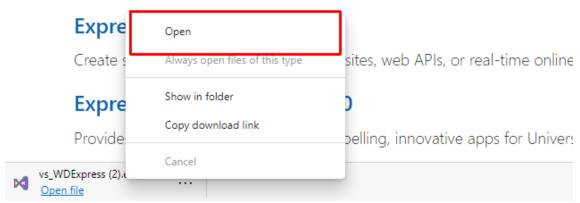

Right click on the WDExpress.exe.

# Still want Visual Studio Express?

# **Express 2017 for Windows Desktop**

Supports building managed and native desktop applications.\*

# **Express 2015 for Windows Desktop**

Supports the creation of desktop applications for Windows.

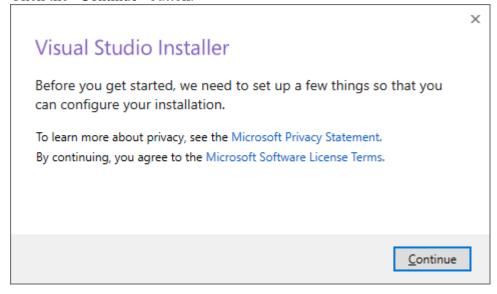

Click the "Continue" button.

Next, follow the on screen windows and accept the default answers.

Click "Next", accept the license agreement. Click "Next".

Visual C# 2010 Express will install. This may take up to twenty minutes depending on your internet connection.

The installed successfully window will be displayed when Visual C# Express is ready to use.

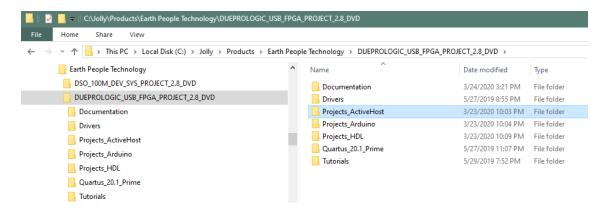

The Active Host Application Software will allow the user to create a custom applications on the PC using the EndTerms to perform Triggers and Data Transfer to/from the DueProLogic. The methods and parameters of the Active Host library are explained in the Active Host Application section. Locate the \Projects\_ActiveHost folders on the EPT FPGA Development System DVD.

# **3 FPGA Active Transfer Library**

The Active Transfer Library is an HDL library designed to transfer data to and from the DueProLogic via High Speed (480 MB/s) USB. It is a set of pre-compiled HDL files

that the user will add to their project before building it. The description of what the library does and how to use its components are described in this manual.

# 3.1 EPT Active Transfer System Overview

The Active Transfer System components consist of the following:

- active\_serial\_library.v

- ft\_245\_state\_machine.v

- endpoint\_registers.vqm

- active\_trigger.v

- active\_transfer.v

- active block.v

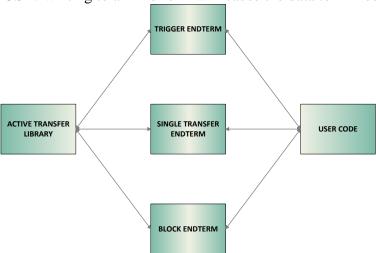

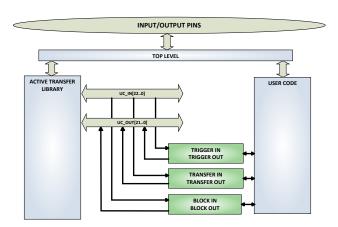

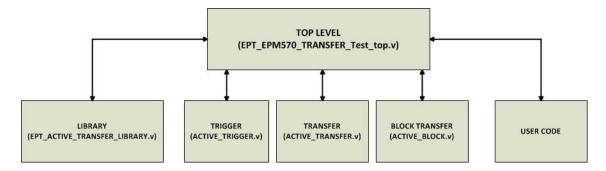

The Active\_Serial\_Library provides the communication to the USB hardware. While separate Input and Output buses provide bi-directional communications with the plug in modules. See the figure below for an overview of the EPT Active\_Transfer system.

### **EPT Active Transfer Library Overview**

Figure 6 shows how the modules of the EPT Active Transfer Library attach to the overall user project. The EPT Active\_Transfer\_Library.vqm, Active\_Trigger.vqm, Active\_Transfer.vqm and Active\_Block.vqm modules are instantiated in the top level of the user project. The User\_Code module is also instantiated in the top level. The Active\_Transfer modules communicate with the User\_Code through module parameters. Each module is a bi-directional component that facilitates data transfer from PC to FPGA. The user code can send a transfer to the Host, and the Host can send a transfer to the user code. This provides significant control for both data transfers and signaling from the user code to PC. The Triggers are used to send momentary signals that can turn on (or off) functions in user code or PC. The Active Transfer is used to send a single byte. And the Active Block is used to send a block of data. The Active\_Transfer and Active\_Block modules have addressing built into them. This means the user can declare up to 8 individual instantiations of Active\_Transfer or Active\_Block, and send/receive data to each module separately.

# 3.2 Active Transfer Library

The Active Transfer Library contains the command, control, and data transfer mechanism that allows users to quickly build powerful communication schemes in the FPGA. Coupled with the Active Host application on the PC, this tools allows users to focus on creating programmable logic applications and not have to become distracted by USB Host drivers and timing issues. The Active Transfer Library is pre-compiled file that the user will include in the project files.

```

//# Copyright Earth People Technology Inc. 2021

//#

//#

//# File Name: EPT_4CE6_AF_Dl_Top.v

//# Author: Earth People Technology

//# Date:

March 14, 2021

//# Revision: A

//#

//# Development: EPT Platform Demonstration Project

//# Application: Altera Cyclone IV FPGA

//# Description: This file contains verilog code which will allow access

//#

to Active Transfer Library.

//#

//#

//#**********************

//# Revision History:

DATE VERSION DETAILS 3/14/21 1 Created

//#

Created

//#

//#

//#

//#

```

);

```

//************************

//* Module Declaration

module EPT 4CE6 AF D1 Top (

CLK 66MHZ,

input wire

RST,

input wire

//UART COMMAND BUS

output wire

UART_OUT, //To external

input wire

UART IN, //From external

XIO 1, //XIO -- UB

output wire [7:0]

input wire [5:0]

XIO 2,

//XIO -- UB

output wire [5:0]

XIO 3,

//XIO -- UB

input wire [5:0]

output wire [5:0]

XIO_4, //XIO -- UB

XIO_5, //XIO -- UB

XIO_6, //XIO -- UB

XIO_7, //XIO -- UB

output wire [31:0]

output wire [3:0]

PB SWITCH 1,

input wire

PB SWITCH 2

input wire

```

The interface from the library to the user code is two uni directional buses, UC\_IN[22:0] and UC\_OUT[20:0]. The UC\_IN[22:0] bus is an output bus (from the library, input bus to the Active Modules) that is used channel data, address, length and control information to the Active Modules. The UC\_OUT[21:0] bus is an input bus (to the library, output bus from the Active Modules) that is used to communicate data, address, length, and control information to the Active Modules.

```

//-----

// Instantiate the EPT Library

//-----

.aa

(aa),

.UART OUT

(UART_OUT),

.UART IN

(uart_txd),

.UC IN

(UC IN),

.UC_OUT

(UC_OUT),

.STATE OUT

(active_serial_state_out),

.TEST OUT

(active_transfer_test_out)

);

```

The UART signals are used to channel data, and control signals to the USB interface chip. These signals are connected directly to input and output pins of the FPGA.

# 3.2.1 Active Trigger EndTerm

The Active Trigger has eight individual self resetting, active high, signals. These signals are used to send a momentary turn on/off command to Host/User code. The Active Trigger is not addressable so the module will be instantiated only once in the top level.

```

743

wire [22*3-1:0] uc out m;

744

eptWireOR # (.N(3)) wireOR (UC OUT, uc out m);

745

active trigger

ACTIVE TRIGGER INST

746

(

747

.uc clk

(CLK 66),

748

.uc reset

(RST),

749

.uc in

(UC IN),

750

.uc out

(uc_out_m[ 0*22 +: 22 ]),

751

752

.trigger to host

(trigger to host),

753

.trigger_to_device

(trigger_in_byte)

754

755

);

```

To send a trigger, decide which bit (or multiple bits) of the eight bits you want to send the trigger on. Then, set that bit (or bits) high. The Active Transfer Library will send a high on that trigger bit for one clock cycle (66 MHz), then reset itself to zero. The bit can stay high on the user code and does not need to be reset to zero. However, if the user sends another trigger using the trigger byte, then any bit that is set high will cause a trigger to occur on the Host side.

```

277

278

// Detect Trigger Out to Host

//-----

279

280

always @(TRIGGER OUT or trigger in reset or reset)

begin

281

282

if(!reset)

283

trigger_to_host = 8'h0;

else if (trigger_in_reset)

284

285

trigger to host = 8'h0;

else if (TRIGGER OUT > 8'h0)

286

287

trigger to host = TRIGGER OUT;

288

end

289

//-----

290

291

// Reset Trigger Out to Host

//-----

292

293

always @ (posedge CLK 66 or negedge reset)

294

begin

295

if(!reset)

296

begin

297

trigger_in_reset <= 0;

298

end

299

else

begin

300

301

if (trigger_to_host > 0)

302

trigger in reset <= 1'b1;

303

else

304

trigger in reset <= 0;

305

end

306

end

```

So, care should be used if the user code uses byte masks to send triggers. It is best to set only the trigger bits needed for a given time when sending triggers.

The user code must be setup to receive triggers from the Host. This can be done by using an asynchronous always block. Whenever a change occurs on a particular trigger bit (or bits), a conditional branch can detect if the trigger bit is for that block of code. Then, execute some code based on that trigger.

```

308

//----

309

// Detect Trigger In

310

//----

311

always @(trigger in byte or trigger in reset or reset)

312

begin

313

if(!reset)

314

begin

315

trigger in detect = 1'b0;

316

end

317

else if (trigger in reset)

318

begin

319

trigger in detect = 1'b0;

320

end

321

else if (trigger in byte > 8'h0)

322

begin

323

trigger in detect = 1'b1;

324

end

325

end

326

327

328

// Store the value of Trigger In

//----

329

330

always @(posedge CLK 66 or negedge reset)

331

begin

332

if(!reset)

333

begin

334

trigger in store <= 8'h0f;

335

trigger in reg <= 1'b0;

336

trigger in reset <= 1'b0;

337

end

338

else if (trigger in detect & !trigger in reg)

339

begin

340

if(trigger in byte != 0)

341

trigger in store[7:0] <= trigger in byte[7:0];</pre>

trigger_in_reg <= 1'b1;</pre>

342

343

end

344

else if (trigger in reg)

345

begin

346

trigger in reg <= 1'b0;

347

trigger in reset <= 1'b1;

348

end

349

else if (!trigger in detect)

350

begin

351

trigger_in_reg <= 1'b0;</pre>

352

trigger in reset <= 1'b0;

353

end

```

#### 3.2.2 Active Transfer EndTerm

The Active Transfer module is used to send or receive a byte to/from the Host. This is useful when the user's microcontroller needs to send a byte from a measurement to the Host for display or processing. The Active Transfer module is addressable, so up to eight individual modules can be instantiated and separately addressed.

```

ACTIVE TRANSFER INST

active_transfer

758

日

(

759

.uc clk

(CLK 66),

760

.uc reset

(reset).

761

.uc in

(UC IN),

762

.uc out

(uc_out_m[ 1*22 +: 22 ]),

763

764

.start transfer

(transfer out reg),

765

.transfer received

(transfer in received),

766

767

.uc addr

(3'h2),

768

.transfer_to_host

769

(transfer out byte),

770

.transfer_to_device

(transfer_in_byte)

771

):

772

```

To send a byte to the Host, select the appropriate address that corresponds to an address on Host side. Place the byte in the "transfer\_to\_host" parameter, then strobe the "start\_transfer" bit. Setting the "start\_transfer" bit to high will send one byte from the "transfer\_to\_host" byte to the Host on the next clock high signal (66 MHz). The "start\_transfer" bit can stay high for the duration of the operation of the device, the Active Transfer module will not send another byte. In order to send another byte, the user must cycle the "start\_transfer" bit to low for a minimum of one clock cycle (66 MHz). After the "start\_transfer" bit has been cycled low, the rising edge of the bit will cause the byte on the "transfer to host" parameter to transfer to the host.

```

181

182

// Transfer byte to Device

183

//-----

184

always @ (TRANSFER OUT EN or reset)

185

begin

186

if(!reset)

187

begin

188

transfer out detect = 1'b0;

189

end

190

else

191

begin

192

if(transfer to device reset)

193

transfer out detect = 1'b0;

194

else if (TRANSFER OUT EN)

195

196

transfer out byte = TRANSFER OUT BYTE;

197

transfer out detect = 1'b1;

198

end

199

end

200

end

201

202

203

// Reset transfer to device reset

//-----

204

205

always @ (posedge CLK 66 or negedge reset)

206

begin

207

if (!reset)

208

begin

209

transfer_to_device_reset <= 1'b0;

210

end

211

else

212

begin

213

if(transfer out detect)

214

transfer to device reset <= 1'b1;

215

216

transfer to device reset <= 1'b0;

217

end

218

end

```

To receive a byte, the Active Host will send a byte using it's SDK. The user code must monitor the transfer\_received port. The transfer\_received port will assert high for one clock cycle (66 MHz) when a byte is ready for reading on the transfer\_to\_device port. User code should use an asynchronous always block to detect when the transfer\_received port is asserted. Upon assertion, the user code should read the byte from the transfer\_to\_device port into a local register.

```

220

//-----

221

// Transfer to Host

222

//-----

223

always @ (posedge CLK 66 or negedge reset)

begin

224

225

if (!reset)

226

白

begin

227

transfer_out <= 1'b0;

228

transfer_out_reg <= 1'b0;

transfer out byte <= 8'h0;

229

230

end

231

else

232

begin

233

if(start_transfer_byte & !transfer_out)

234

begin

235

transfer out byte <= TRANSFER HOST BYTE;

236

transfer_out_reg <= 1'b1;

237

transfer out <= 1'b1;

238

239

else if(start_transfer_byte & transfer_out)

240

begin

241

transfer out reg <= 1'b0;

transfer out <= 1'b1;

242

243

end

244

else if (!start transfer byte & transfer out)

245

白

246

transfer_out_reg <= 1'b0;

transfer out <= 1'b0;

247

248

end

249

end

250

end

```

#### 3.2.3 Active Block EndTerm

The Active Block module is designed to transfer blocks of data between Host and User Code and vice versa. This allows buffers of data to be transferred with a minimal amount of code. The Active Block module is addressable, so up to eight individual

modules can be instantiated and separately addressed. The length of the block to be transferred must also be specified in the uc\_length port.

```

811

active block

BLOCK TRANSFER INST

812

(

813

.uc clk

(CLK 66),

814

.uc reset

(RST),

815

.uc in

(UC IN),

816

.uc out

(uc out m[ 2*22 +: 22 ]),

817

818

.start transfer

(block_out_reg),

819

.transfer received

(block in rcv),

820

821

.transfer ready

(block byte ready),

822

823

.uc addr

(3'h4),

824

.uc length

(BLOCK COUNT 8),

825

826

.transfer to host

(block out byte),

.transfer to device

(block in data),

827

828

829

.STATE OUT

(block state out),

830

.TEST BUS

(block out test bus)

831

832

);

```

To send a block, it's best to have buffer filled in a previous transaction, Then assert the start\_transfer bit. This method is opposed to collecting and processing data bytes after the start\_transfer bit has been asserted and data is being sent to the Host.

Once the buffer to send is filled with the requisite amount of data, the address and buffer length should be written to the uc\_addr and uc\_length ports. Set the start\_transfer bit high, the user code should monitor the transfer\_ready port. At the rising edge of the transfer\_ready port, the byte at transfer\_to\_host port is transferred to the USB chip. Once this occurs, the user code should copy the next byte in the buffer to transfer\_to\_host port. On the next rising edge of transfer-ready, the byte at transfer\_to\_host will be transferred to the USB chip. This process continues until the number of bytes desicribed by the uc\_length have been transferred into the USB chip.

```

542

543

// Registers to start Block Transfer Out

544

545

always @ (posedge CLK 66 or negedge RST)

546

begin

547

if(!RST)

548

begin

549

block out reg <= 1'b0;

550

start block transfer reg <= 1'b0;

551

end

552

else

553

begin

554

if(start_block_transfer & !start_block_transfer_reg)

555

start block transfer reg <= 1'b1;

556

else if(start_block_transfer_reg & !block_out_reg)

557

begin

558

block out reg <= 1'b1;

559

end

else if(block_out_counter >= BLOCK_COUNT_8)

560

561

begin

562

block_out_reg <= 1'b0;

563

start block transfer reg <= 1'b0;

564

end

565

end

end

566

567

568

569

// Data for Block Transfer Out

570

//-----

571

always @ (posedge CLK 66 or negedge RST)

572

□ begin

573

if(!RST)

574

begin

575

block_out_counter <= 0;

576

end

577

else

578

begin

579

if(block_byte_ready)

580

begin

581

block out counter <= block out counter + 1'd1;

582

583

else if(block out counter >= BLOCK COUNT 8 )

584

begin

585

block_out_counter <= 0;

586

587

end

588

```

To receive a buffer from the Host, the user code should monitor the transfer\_received port for assertion. When the bit is asserted, the next rising edge of transfer\_ready will indicate that the byte at transfer\_to\_device is ready for the user code to read.

[Add code snippet showing Active Block Module bytes received by the user code]

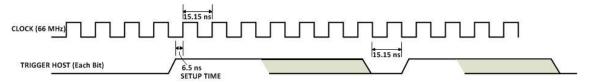

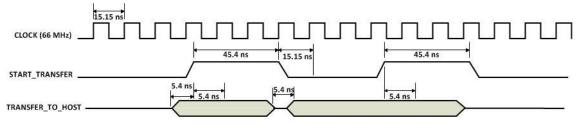

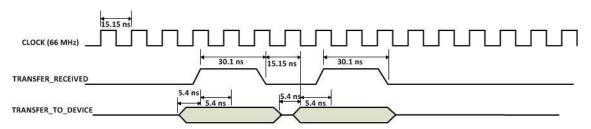

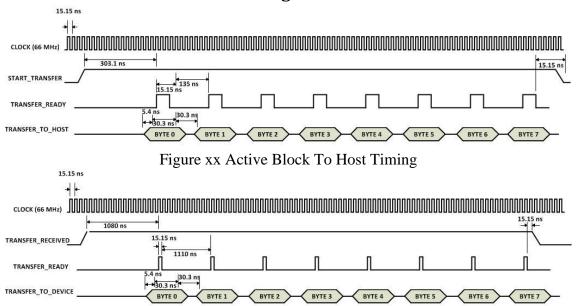

# 3.3 Timing Diagram for Active Transfer EndTerms

The Active Transfer Library uses the 66 MHz clock to organize the transfers to Host and transfer to Device. The timing of the transfers depends on this clock and the specifications of the USB chip. Users should use the timing diagrams to ensure proper operation of user code in data transfer.

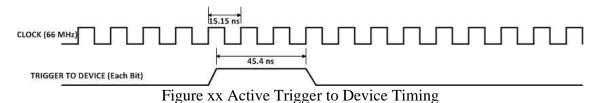

# 3.3.1 Active Trigger EndTerm Timing

Figure xx Active Trigger to Host Timing

# 3.3.2 Active Transfer EndTerm Timing

Figure xx Active Transfer To Host Timing

Figure xx Active Transfer To Device Timing

# 3.3.3 Active Block EndTerm Timing

Figure xx Active Block To Device Timing

# 4 Compiling, Synthesizing, and Programming FPGA

The FPGA on the EPT-4CE6-AF-D2 can be programmed with the Active Transfer Library and custom HDL code created by the user. Programming the FPGA requires the use of the Quartus Prime software and a standard USB cable. There are no extra parts to buy, just plug in the USB cable. Once the user HDL code is written according to the syntax rules of the language (Verilog and VHDL) it can be compiled and synthesized using the Quartus Prime software. This manual will not focus on HDL coding or proper coding techniques, instead it will use the example code to compile, synthesize and program the FPGA.

# 4.1 Setting up the Project and Compiling

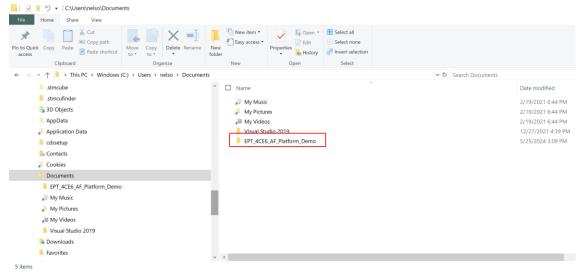

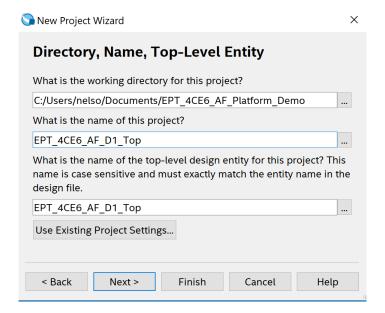

Once the HDL code (Verilog or VHDL) is written and verified using a simulator, a project can be created using Quartus Prime. Writing the HDL code and simulating it will be covered in later sections. Bring up Quartus Prime, then use Windows Explorer to browse to C:\Users\nelso\Documents\ to create a new directory called: "EPT\_4CE6\_AF\_Platform\_Demo".

(Quartus

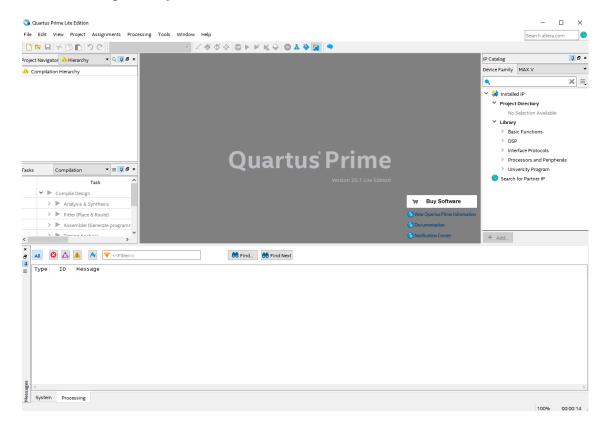

Open Quartus Prime by clicking on the icon.

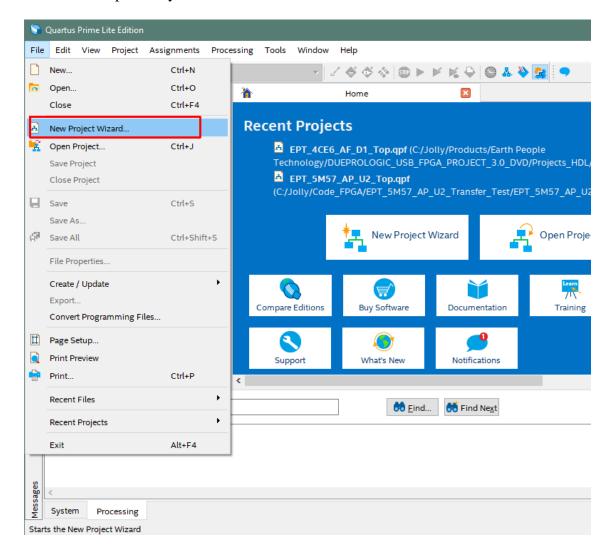

Under Quartus, Select File->New Project Wizard. The Wizard will walk you through setting up files and directories for your project.

At the Top-Level Entity page, browse to the

C:\Users\nelso\Documents\ EPT\_4CE6\_AF\_Platform\_Demo

directory to store your project. Type in a name for your project "EPT\_4CE6\_AF\_D1\_Top".

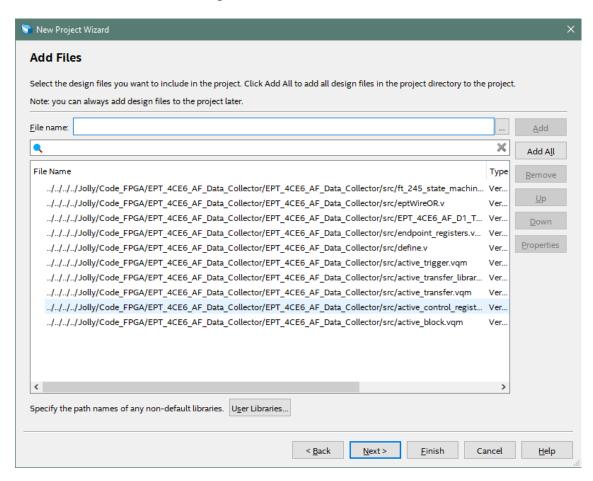

Select Next. At the Add Files window: Browse to the

Projects\_HDL\EPT\_4CE6\_AF\_Platform\_Demo\src

folder of the EPT FPGA Development System DVD. Copy the files from the \src directory.

- active block.v

- active\_transfer.v

- active\_trigger.v

- active\_transfer\_uart.v

- active\_serial\_library.v

- define.v

- ft\_245\_state\_machine.v

- endpoint\_registers.v

- eptWireOr.v

- flipflop.v

- image\_block\_in.v

- image\_ept\_logo.v

- image\_face\_1.v

- image\_tri\_wave.v

- led\_update.v

- lfsr.v

- mux.v

- read\_control\_logic.v

- serial\_clock.v

- sync\_fifo.v

- uart\_receiver.v

- uart\_top.v

- uart\_transmitter.v

- write\_control\_logic.v

- EPT\_4CE6\_AF\_D1\_Top.v

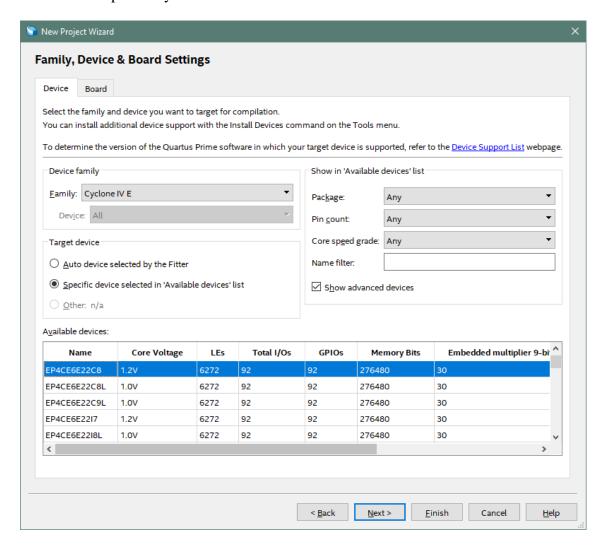

Select Next, at the Device Family group, select Cyclone IV for Family. In the Available Devices group, browse down to EP4CE6E22C8 for Name.

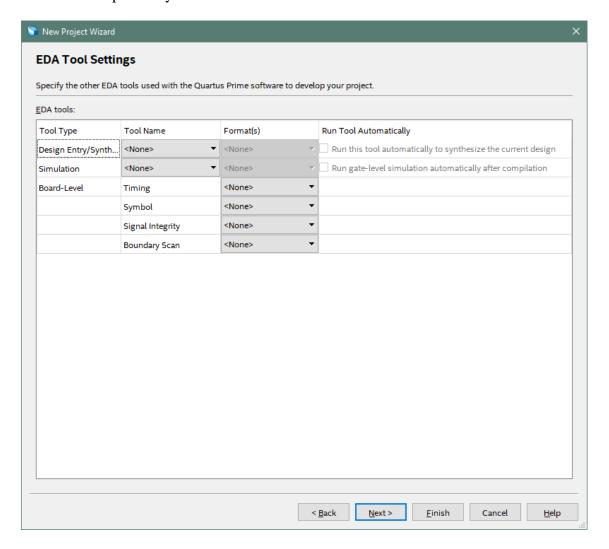

Select Next, leave defaults for the EDA Tool Settings.

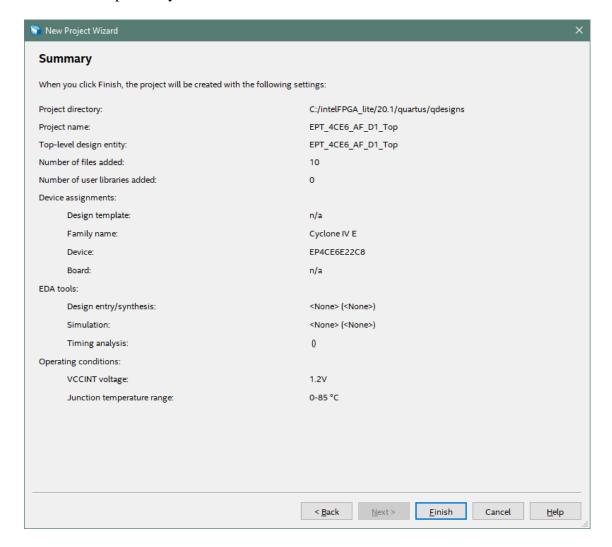

Select Next, then select Finish. You are done with the project level selections.

Next, we will select the pins and synthesize the project.

## 4.1.1 Selecting Pins and Synthesizing

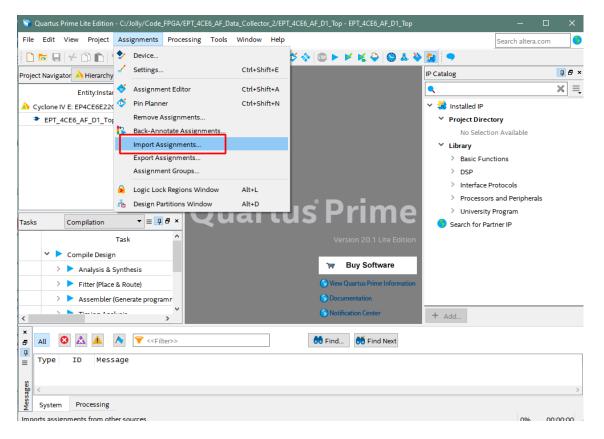

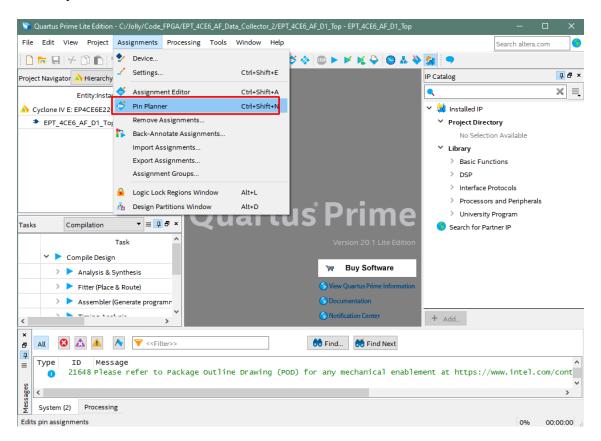

With the project created, we need to assign pins to the project. The signals defined in the top level file (in this case: EPT\_4CE6\_AF\_D1\_Top.v) will connect directly to pins on the FPGA. The Pin Planner Tool from Quartus Prime will add the pins and check to verify that our pin selections do not violate any restrictions of the device. In the case of this example we will import pin assignments that created at an earlier time. Under Assignments, Select Import Assignments.

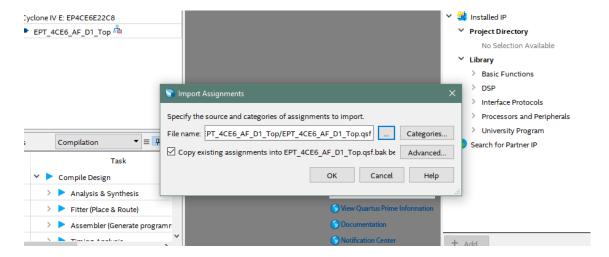

At the Import Assignment dialog box, Browse to the \Projects\_HDL\EPT\_Transfer\_Demo \ EPT\_4CE6\_AF\_D1\_TOP folder of the EPT FPGA Development System DVD. Select the "EPT\_4CE6\_AF\_D1\_Top.qsf" file.

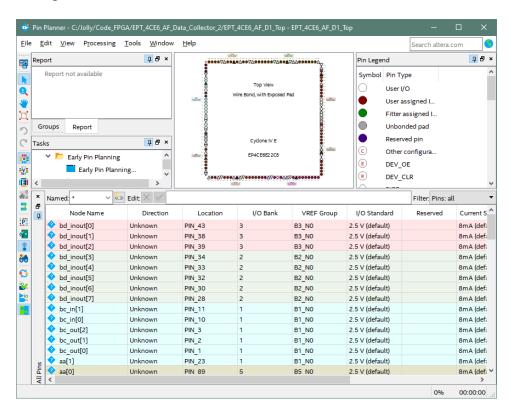

Click Ok. Under Assignments, Select Pin Planner. Verify the pins have been imported correctly.

The pin locations should not need to be changed for EPT USB FPGA Development System. However, if you need to change any pin location, just click on the "location" column for the particular node you wish to change. Then, select the new pin location from the drop down box.

Exit the Pin Planner. Next, we need to add the Synopsys Design Constraint file. This file contains timing constraints which forces the built in tool called TimeQuest Timing Analyzer to analyze the path of the synthesized HDL code with setup and hold times of the internal registers. It takes note of any path that may be too long to appropriately meet the timing qualifications. For more information on TimeQuest Timing Analyzer, see

### Quest Timing Analyzer Quick Start Guide

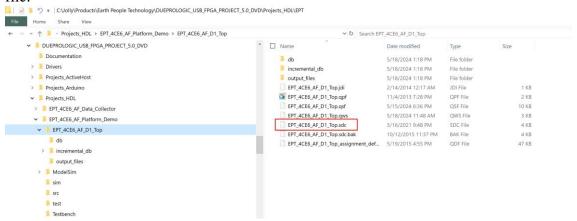

Browse to the \Projects\_HDL\EPT\_Platform\_Demo \ EPT-4CE6-AF-D1\_TOP folder of the EPT FPGA Development System DVD. Select the "EPT\_4CE6\_AF\_D1\_Top.sdc" file.

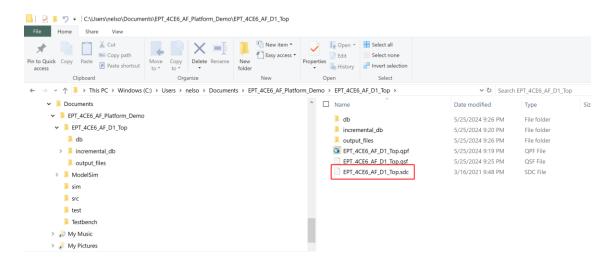

Copy the file and browse to

C:\Users\nelso\Documents\EPT\_4CE6\_AF\_Platform\_Demo \ EPT\_4CE6\_AF\_D1\_Top directory. Paste the file.

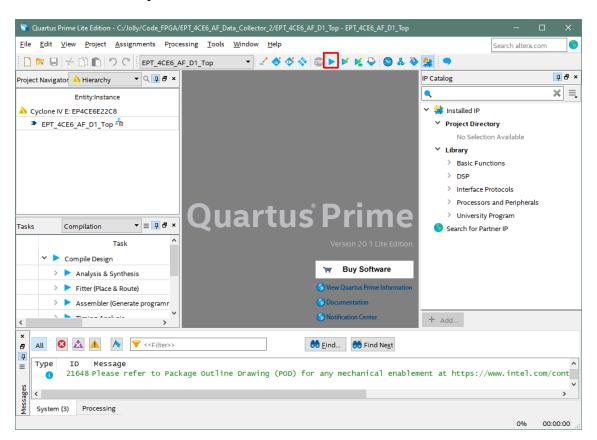

### Select the Start Compilation button.

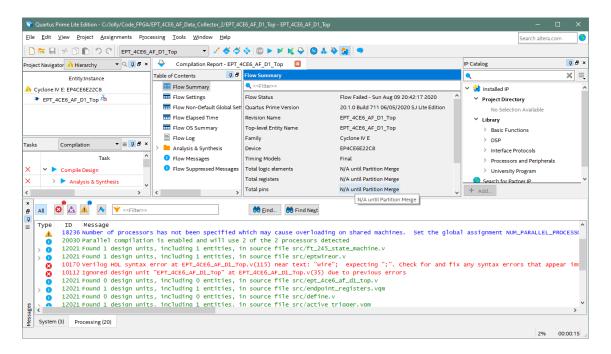

If you forget to include a file or some other error you should expect to see a screen similar to this:

Click Ok, the select the "Error" tab to see the error.

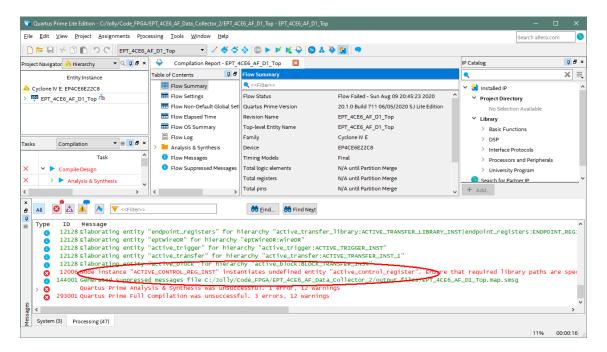

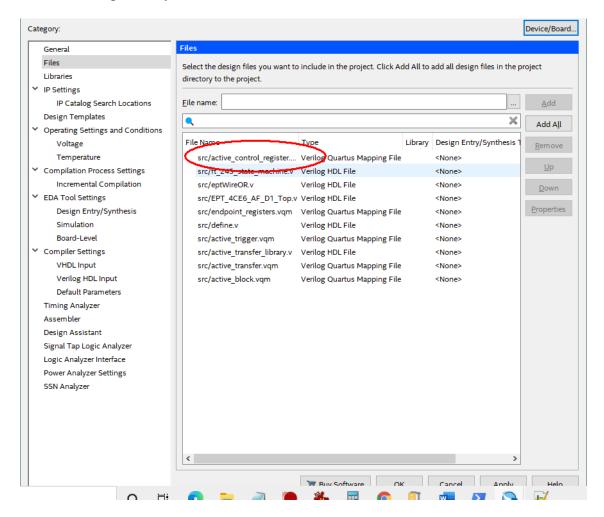

The error in this case is the missing file "active\_control\_register". Click on the Assignment menu, then select Settings, then select Files. Add the "active\_control\_register.v" file from the database.

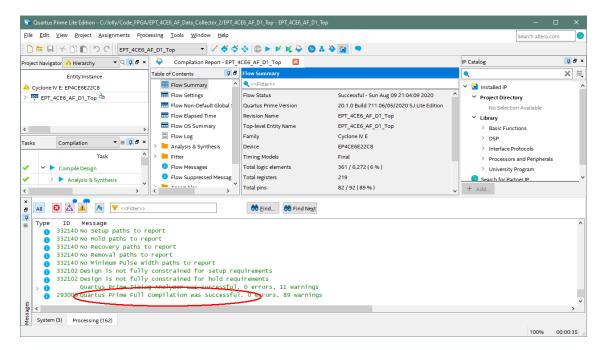

Click Ok then re-run the Compile process. After successful completion, the screen should look like the following:

At this point the project has been successfully compiled, synthesized and a programming file has been produce. See the next section on how to program the FPGA.

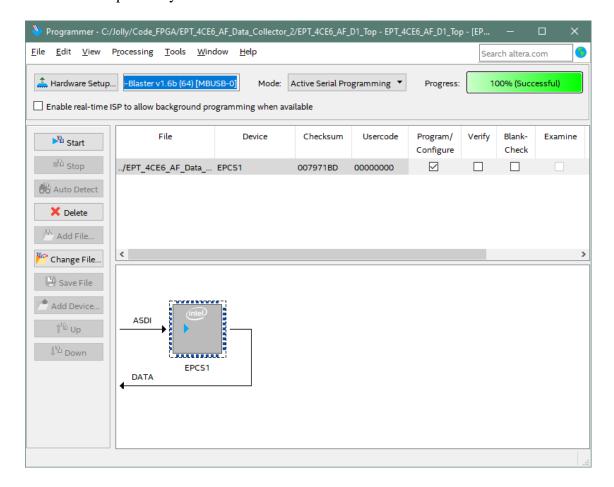

## 4.1.2 Configuring the FPGA

Configuring the FPGA is quick and easy. All that is required is a standard USB-C cable and the EPT\_Blaster Driver DLL. Connect the DueProLogic to the PC, open up Quartus Prime, open the programmer tool, and click the Start button. To program the DPL Configuration Flash, follow the steps to install the USB Driver and the JTAG Driver Insert for Quartus Prime.

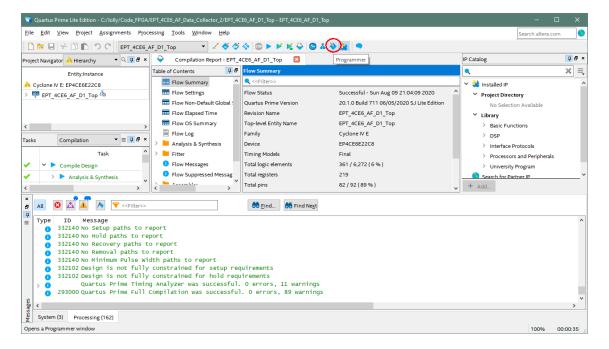

If the project created in the previous sections is not open, open it. Click on the Programmer button.

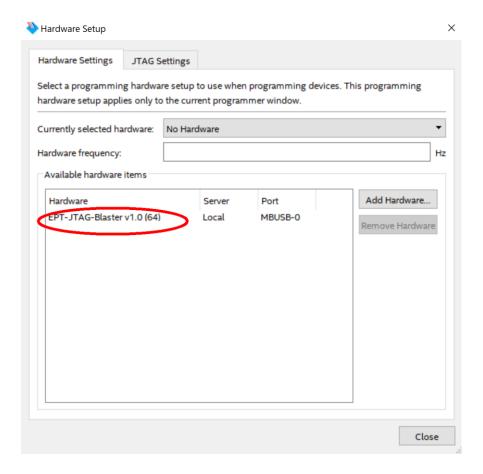

The Programmer Window will open up with the programming file selected. Click on the Hardware Setup button in the upper left corner.

The Hardware Setup Window will open. In the "Available hardware items", double click on "EPT-Blaster v1.0".

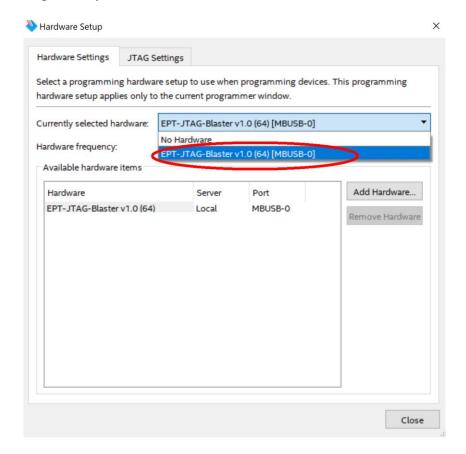

If you successfully double clicked, the "Currently selected hardware:" dropdown box will show the "EPT-Blaster v1.0 (64)".

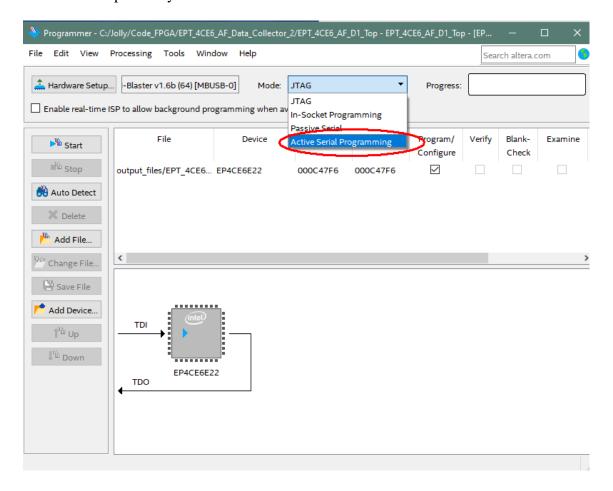

Click on the "Mode:" drop down box. Select the "Active Serial Programming" option.

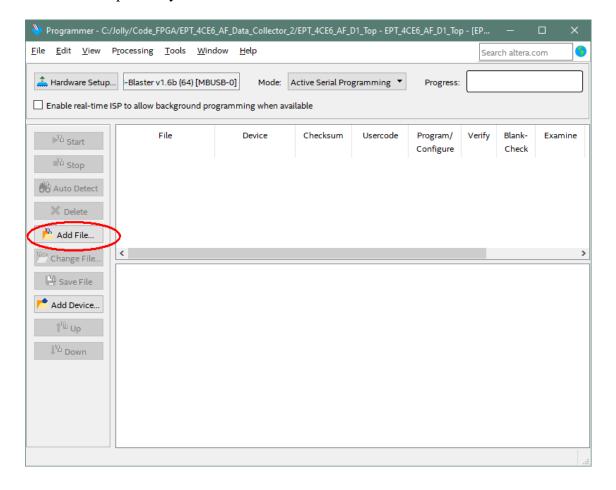

Click on the "Add File" button

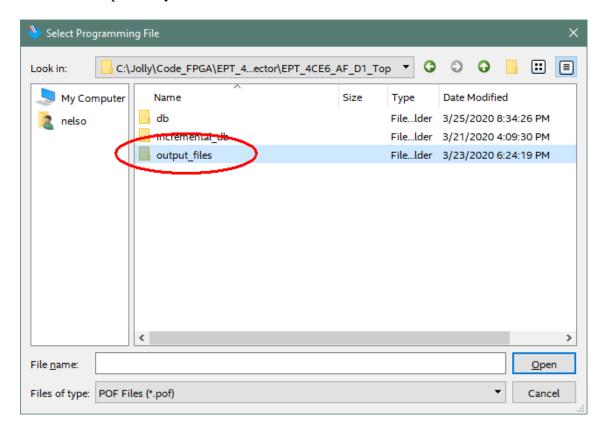

At the Browse window, double click on the output files folder.

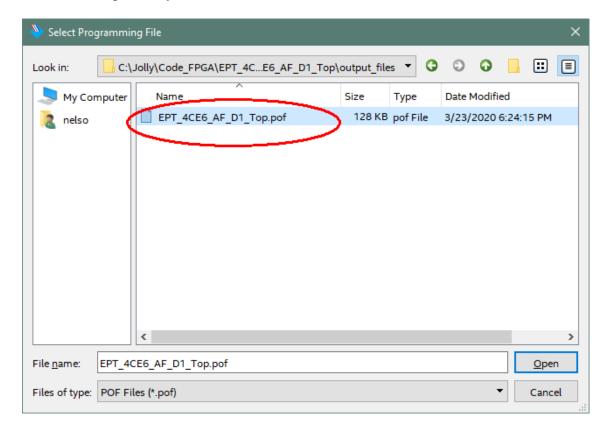

Double click on the "EPT\_4CE6\_D1\_Top.pof" file. Click the Open button in the lower right corner.

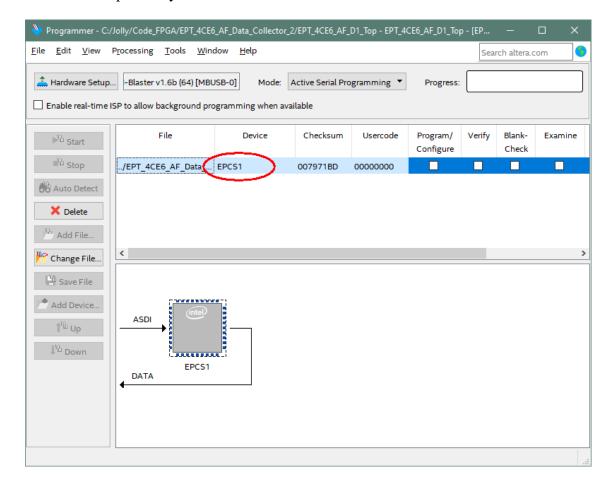

Select the EPCS1 under "Device".

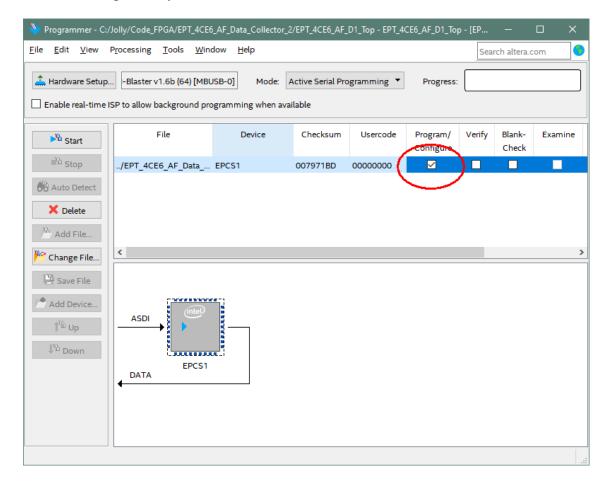

Next, selet the checkbox under the "Program/Configure" of the Programmer Tool.

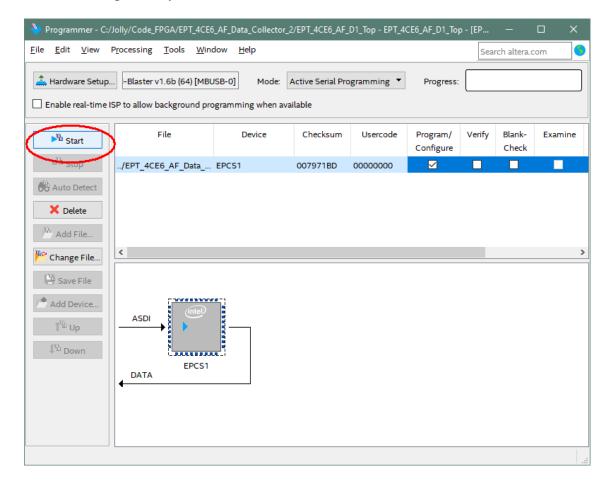

Click on the Start button to to start programming the FPGA. The Progress bar will indicate the progress of programming.

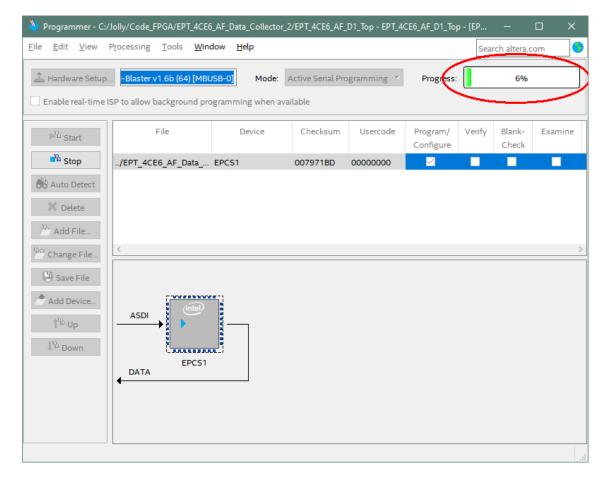

The programming of the DueProLogic will start and you can check the progress in the "Progress" Bar.

When the programming is complete, the Progress bar will indicate success.

At this point, the DueProLogic is programmed and ready for use. To test that the FPGA is properly programmed, bring up the Platform Demo Tool. Click on one of the LED's and verify that the LED selected lights up. Press one of the switches on the board and ensure that the switch is captured on the Platform Demo Tool. Now you are ready to connect to the Arduino Due and write some code to transfer data between microcontroller and PC.

# 5 Active Host Application

The Active Host SDK is provided which allows easy interface to application software written in C#. It runs on the PC and provides transparent connection from PC application code through the USB driver to the user FPGA code. The user code connects to "Endterms" in the Active Host SDK. These host "Endterms" have

complementary HDL "Endterms" in the Active Transfer Library. Users have seamless bi-directional communications at their disposal in the form of:

- Trigger Endterm

- Transfer Endterm

- Block Endterm